- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MC_RGM_DBRE register configuration

MC_RGM_DBRE register configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MC_RGM_DBRE register configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working on SPC5746C MCU and I have few observations and doubts on power on reset concept in this MCU.

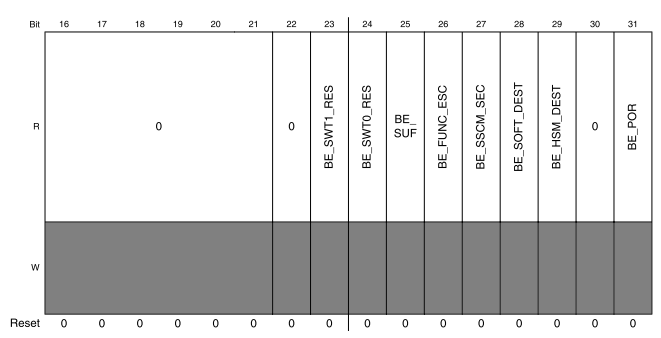

1. As per the datasheet, we can control the reset generation for POR.

MC_RGM_DBRE[BE_POR] bit is 0x00, RESET will be generated.

MC_RGM_DBRE[BE_POR] bit is 0x01, RESET will not be generated.

Please correct me if I am wrong.

2. For example, if I configured the MC_RGM_DBRE register to do not generate RESET to MCU. But, the PORST line status is changing from high to low and low to high (based on power status). Will it don't cause MCU RESET?

3. Can I observe the PORST line status (is it reflecting to any register) ?

4. If any register is reflecting the status of PORST line status. When it will be set/1 and when it will be reset/0.

Can you guys clarify my doubts.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Things are quite different from what you explained.

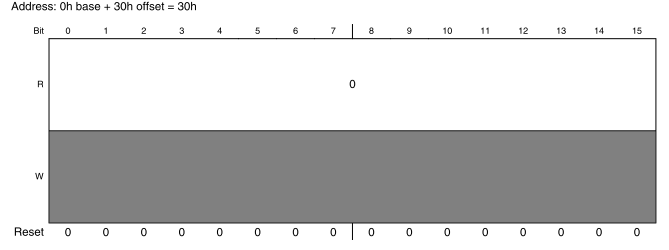

as you can see you cannot configure this register as the write option is greyed out:

Any reset will be reflected on reset bidirectional pin.

3. Can I observe the PORST line status (is it reflecting to any register) ?

No, even if you can you will always read 1. What is the point to do this?

4. If any register is reflecting the status of PORST line status. When it will be set/1 and when it will be reset/0.

When the device is not powered it will be set to 0.

regards,

Peter