- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX8QM ENET_REFCLK_125MHz source?

i.MX8QM ENET_REFCLK_125MHz source?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

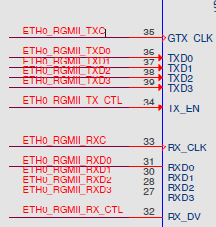

I'm designing and RGMII interface for a 1000BASE-T1 PHY and understand that ENET_RGMII_TXC is an output to provide a 125MHz signal to the PHY.

On the i.MX6, this 125MHz clock could be provided externally or routed from GPIO16. Is there an equivalent internal clock reference on the i.MX8 or do I need to provide this with an external crystal on the ENET_REFCLK_125MHz pin? I can't find anything in the reference manual to help. Thanks!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

ENETx_RGMII_TXC will be shown as RMII_REF_CLK in RMII mode.

There is no RGMII_REF_CLK more.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Customers can use the connection scheme below for the RGMII.

There is no need for special reference clock settings additionally to standard

ones for i.MX8 ENET in RGMII mode.Internal clock is used.

Have a great day,

Yuri

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

Thanks for the clarification. I found the details of the USB 125MHz internal clock on the reference manual, but couldn't find anything about an internal Ethernet clock.

What is the recommended method of termination for the ENET0/1_REFCLK_125M_25M pins (B10 and A11) then if the internal clock is used? Just leave them floating?

Do you have an estimated date when the updated release documentation will be available for the i.MX8QM?

Regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

ENETx_REFCLK_125M_25M is reference clock for external PHY if needed.

I do not know exact schedule for documentation publishing, but hope - soon.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

Thank you. In which case the Reference Manual may need updating as it lists these 2 pins as inputs, not outputs, and the description contradicts itself, describing them as "providing a 125MHz external reference clock input." which is confusing.

Reference Manual on pg 3499 (iMX8QM_RM_Rev_E)

Regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

ENETx_RGMII_TXC will be shown as RMII_REF_CLK in RMII mode.

There is no RGMII_REF_CLK more.

Regards,

Yuri.