- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso SDK

- :

- Available modes for peripherals configuration

Available modes for peripherals configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Available modes for peripherals configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

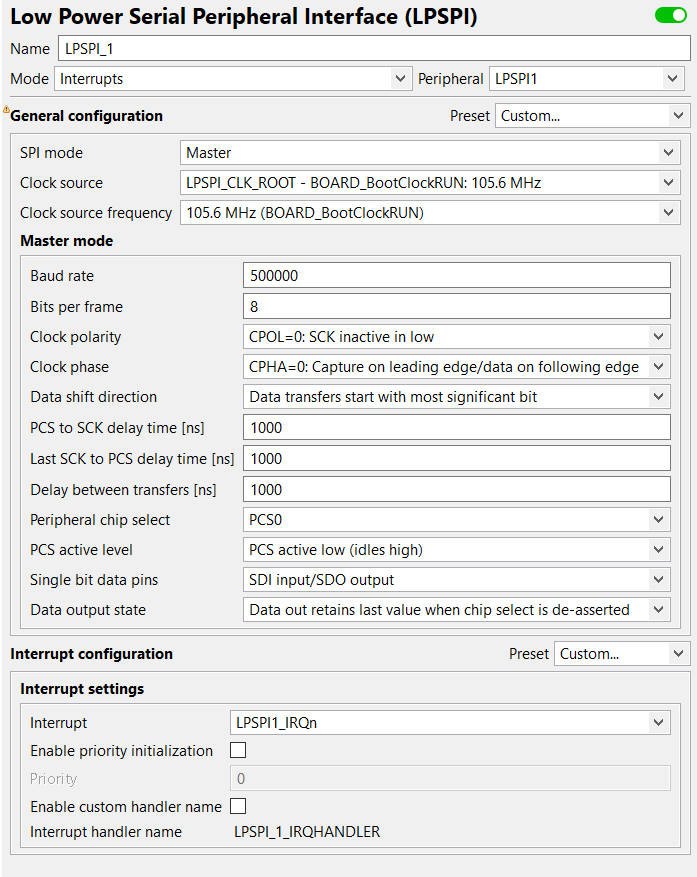

We are working with the SDK_2.6.2 version for MIMXRT1062xxxxA processor on a MIMXRT1060-EVK and I have a few questions regarding the available configuration modes for peripherals inside MCUXpresso Config Tools.

For example, each instance of the LPSPI peripheral has 5 user configurable modes (Polling, Interrupts, Transfer, eDMA and FreeRTOS). I have understood from the API Reference Manual that the Polling mode requires the use of the transfer blocking functions, while an Interrupt mode uses a non blocking data transfer.

However, when using a TransferNonBlocking function, the structure named handle, passed as a second parameter to the function, has fields which are configurable inside the Transfer tab only (e.g: Continuous PCS signal or Swap bytes option in case of a Slave instance). If in Interrupt mode, how can I change the default values for these fields inside MCUXpresso Config Tools?

Is the Transfer mode used only for a blocking type of data transfer? If not in Interrupt mode, the generated code in the peripherals.c file does not include the call of the EnableIRQ function.

Could you briefly explain each mode - I'd like to know what use-cases they have.

Thank you in advance,

Irina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Irina,

First of all, sorry for the later reply.

About Interrupt transfer mode, there with a demo named [interrupt_b2b\master] with below path:

..\boards\evkmimxrt1060\driver_examples\lpspi\interrupt_b2b\master

It will call below structure to define master configuration, such as:

/*Master config*/

masterConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.bitsPerFrame = 8;

masterConfig.cpol = kLPSPI_ClockPolarityActiveHigh;

masterConfig.cpha = kLPSPI_ClockPhaseFirstEdge;

masterConfig.direction = kLPSPI_MsbFirst;

masterConfig.pcsToSckDelayInNanoSec = 1000000000 / masterConfig.baudRate;

masterConfig.lastSckToPcsDelayInNanoSec = 1000000000 / masterConfig.baudRate;

masterConfig.betweenTransferDelayInNanoSec = 1000000000 / masterConfig.baudRate;

masterConfig.whichPcs = EXAMPLE_LPSPI_MASTER_PCS_FOR_INIT;

masterConfig.pcsActiveHighOrLow = kLPSPI_PcsActiveLow;

masterConfig.pinCfg = kLPSPI_SdiInSdoOut;

masterConfig.dataOutConfig = kLpspiDataOutRetained;

srcClock_Hz = LPSPI_MASTER_CLK_FREQ;

LPSPI_MasterInit(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

As my understanding about Transfer mode, which is a higher level of polling/interrupt/DMA mode.

In fact, Transfer mode still need to call one of polling/interrupt/DMA mode related transactional API function.

Thanks for the attention.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hui_Ma,

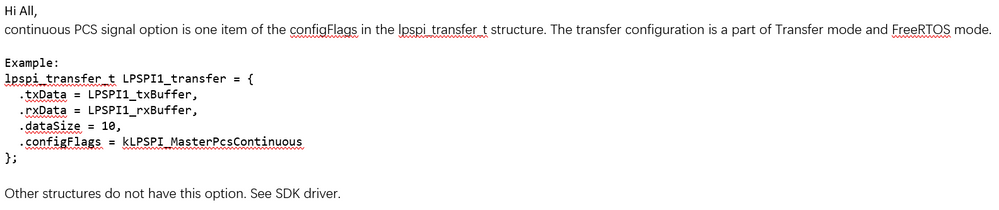

I have another question regarding this topic - why can't we use continuous mode on SPI in interrupt mode (only available in transfer mode) ?

Am I missing something? How can we achieve that functionality with only these settings available?

Thank you in advance for answering to these questions.

Kind regards,

Razvan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think the LPSPI component Mode setting is correct.

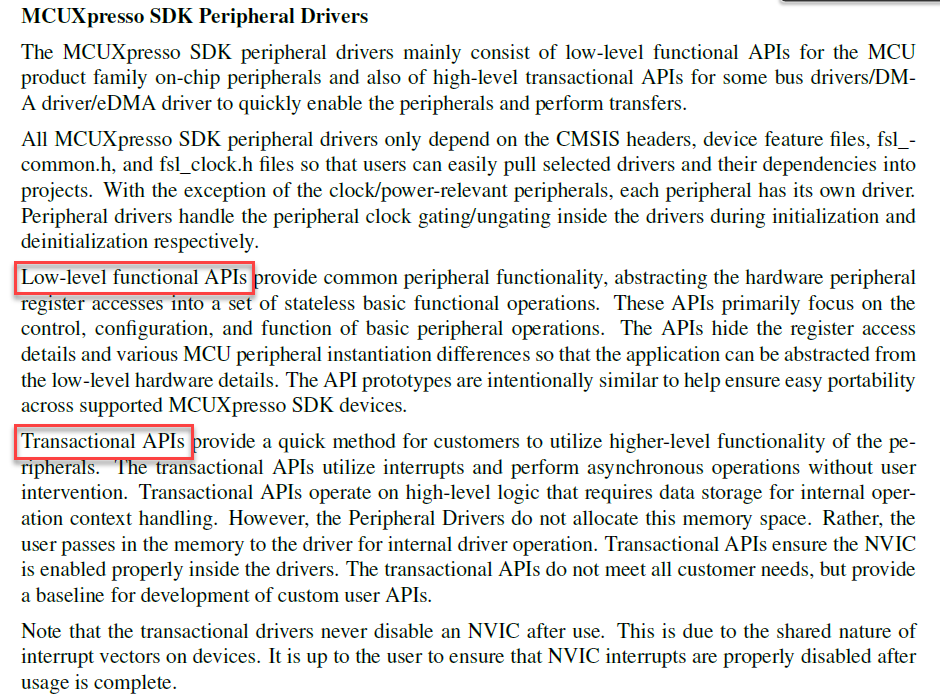

The SDK peripheral drivers has two level functional APIs:

The Transfer mode using transcational API, which based on LPSPI driver provided

LPSPI_MasterTransferBlocking() or LPSPI_MasterTransferNonBlocking() API functions.

So, the Continuous SCK available for transfer mode.

While, the interrupt and polling mode, just provide low level function API, customer need to write their required transcational API based low-level driver. So, customer need to enable continuous SCK feature with their transactional API function manually.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hui_Ma,

So you are saying that MCUX with CT does not let you work in interrupt mode and also have all the options available - am I right? Let me explain why I find that curious - as you said, 'transfer mode' is on a higher level API than 'interrupt mode' so, for me at least, it makes more sense to have the same or even more hardware options available as you go lower (although I understand that higher level abstraction can sometimes mean less fine grain control).

Thank you for your answers.

Kind regards,

Razvan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Razvan,

When you check MCUXpresso CT tool generated code with LPSPI interrupts mode, which using below LPSPI init functinon:

void LPSPI_1_init(void) {

LPSPI_MasterInit(LPSPI_1_PERIPHERAL, &LPSPI_1_config, LPSPI_1_CLOCK_FREQ);

/* Enable interrupt LPSPI1_IRQn request in the NVIC */

EnableIRQ(LPSPI_1_IRQN);

}

It just do the LPSPI initialization and enable LPSPI related IRQ at NVIC.

So, cusotmer also still need to call <fsl_lpspi.c> & <fsl_lpspi.h> driver to realise the data transfer.

Just as [lpspi_interrupt_b2b_master] demo showed, when using MCUXpresso CT generated interrupt mode code,

customer need to call below code to do data transfer:

/*TCR is also shared the FIFO , so wait for TCR written.*/

while (LPSPI_GetTxFifoCount(EXAMPLE_LPSPI_MASTER_BASEADDR) != 0)

{

}

/*Fill up the TX data in FIFO */

while ((LPSPI_GetTxFifoCount(EXAMPLE_LPSPI_MASTER_BASEADDR) < g_masterFifoSize) &&

(masterTxCount - masterRxCount < g_masterFifoSize))

{

/*Write the word to TX register*/

LPSPI_WriteData(EXAMPLE_LPSPI_MASTER_BASEADDR, masterTxData[masterTxCount]);

++masterTxCount;

if (masterTxCount == TRANSFER_SIZE)

{

break;

}

}

LPSPI_EnableInterrupts(EXAMPLE_LPSPI_MASTER_BASEADDR, kLPSPI_RxInterruptEnable);

Daniel had written a document to show how to using [peripheral] component with MCUXpresso CT tool:

https://community.nxp.com/docs/DOC-341986

Wish it helps.

best regards,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hui_Ma,

I think you misunderstood me - I am saying that you can use spi interrupt mode, but you don't have access to all settings for it, like enabling continuous mode. I am not sure what you wanted to show with the code snippets or with Daniel Chen's document - which I like, but does not help in clarifying the spi interrupt mode - continuous mode enabling problem.

Kind regards,

Razvan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Razvan,

Thanks for highlighting the [continuous chip select mode enaaling] option with LPSPI interrupt mode.

I need to check that feature with MCUXpresso CT tool design team.

I will update when there with any feedback. Thanks for the patience.

best regards,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mike,

Thank you as well for your support on the matter. I'll wait for the other team's response.

Kind regards,

Razvan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Razvan,

I forward an email about this topic, you could check the feedback from MCUXpresso Config Tool design team. Thanks.

best regards,

Mike