- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- What is the max frequency for MCGFFCLK?

What is the max frequency for MCGFFCLK?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the max frequency for MCGFFCLK?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

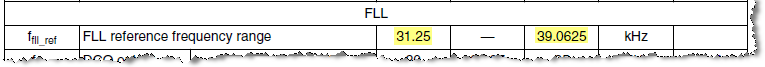

If you aren't using the FLL can the MCGFFCLK be configured to be higher than 39.0625 kHz? I am using an old mcg driver where pll_init() sets the MCGFFCLK to less than 39.0625 kHz even though I am using the PLL not the FLL. The logic is like this:

// the max frequency for the FLL reference is 39.0625kHz so the MCG FF clock should not exceed that

if (crystal_val <= 1250000) {frdiv_val = 0;} // fmax = 1250000/32 = 39062.5

else if (crystal_val <= 2500000) {frdiv_val = 1;} // fmax = 2500000/64 = 39062.5

else if (crystal_val <= 5000000) ...

I didn't chase down the details in the latest KSDK but I did see this comment

* When porting to a new board, set the following members

* according to the board setting:

* 1. frdiv: If the FLL uses the external reference clock, set this

* value to ensure that the external reference clock divided by frdiv is

* in the 31.25 kHz to 39.0625 kHz range.

Here it says *if the FLL uses the external reference* - but I am not using the FLL.

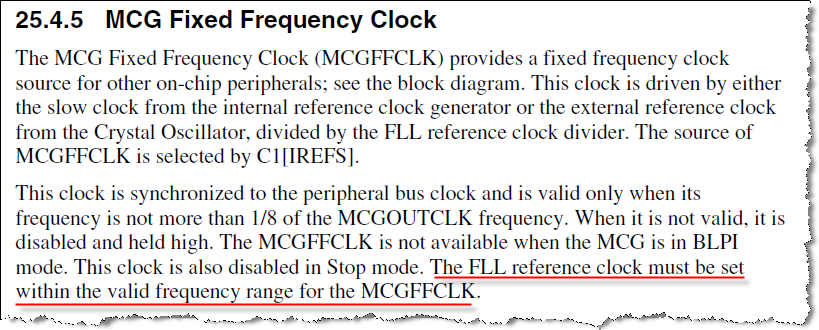

My MCGFFCLK is 23437.5 Hz but I would like to double it so there is an integer number of cycles per second but then it would exceed 39.0625 kHz.

Thanks,

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matt,

Although you only use the PLL mode, the FLL still be used before being configured into the PLL mode.

You must ensure the ffll_ref within FLL reference frequency range.

But maybe you can change the frdiv after the MCG has run into PLL? But this is still to be tested.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

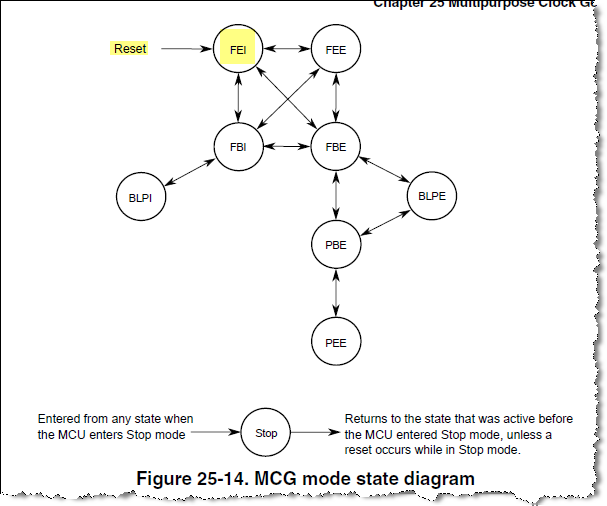

Thanks Robin for the reply. Yeah I would switch FRDIV after the device is already in PEE mode. But the FLL is already disabled in PBE mode:

The FLL is disabled in a lowpower state.

The FLL reference frequency requirement is clear. But if the FLL is disabled in a lowpower state then it's not clear why it would constrain MCFFCLK. But that is the only spec I can find. I don't like to operate out of spec even if it 'seems' to work although I don't see any reason why it shouldn't.

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

My experience with the FLL is that it will continue to oscillate at its natural resonant frequency when the input reference is removed. When the input is there it will cause it to lock to its value but is not needed for the FLL to actually work.

Presumably using an out of range input is similar to not having one and so it will simply oscillate at its natural frequency instead.

If the FLL output is not used (after transitioning to the final clocking state) it is also not of any real interest what the FLL does.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Yeah it doesn't surprise me that that's the case - but in PEE mode the FLL should be disabled in a low power mode so I wasn't concerned what the FLL might do, I was wondering why the MCGFFCLK would still be constrained by the FLL in that case. The requirement on MCGFFCLK is just inferred from its use as fll_ref - but if the FLL is disabled is it 'still' fll_ref and if not then what can it be?

Thanks,

Matt