- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- CKE control of RT1052 SEMC

CKE control of RT1052 SEMC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Guys,

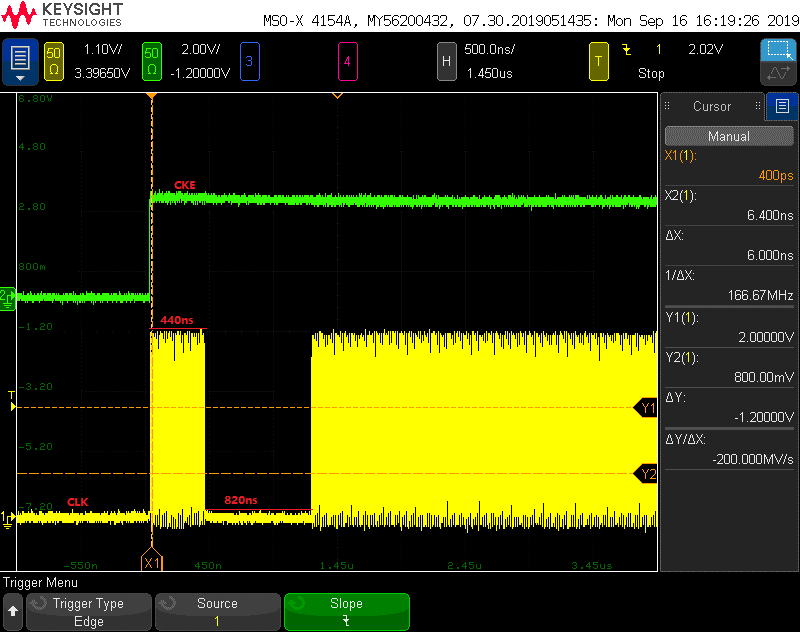

Do you know how to control the CKE and CLK signals from SEMC module? I'm connecting a SDRAM (AS4C8M16S, clock = 72MHz) with it, everything works perfect except for the power up timing of CKE and CLK. As the SDRAM chip requirement, CKE should be pulled high after maintaining a 200us stable CLK, but both signals start up at the same time and somehow CLK is suppressed for a while. I checked RT1050 reference manual and didn't find any register about it (only CKEOFF is mentioned in SDRAMCR1, but I don't think it works for this case).

SEMC settings:

uint32_t ClockCycleNs = 13;

static const uint32_t RefreshCycleNs = (64*1000*1000) / 4096;

sdramconfig.memsize_kbytes = 16MBytes / 1024;

sdramconfig.portSize = kSEMC_PortSize16Bit;

sdramconfig.burstLen = kSEMC_Sdram_BurstLen8;

sdramconfig.columnAddrBitNum = GetColBitsFromNum( 9 );

sdramconfig.casLatency = GetCasLatencyFromNum( 3 );

sdramconfig.tPrescalePeriod_Ns = 1 * (16 * ClockCycleNs);

sdramconfig.tPrecharge2Act_Ns = 30;

sdramconfig.tAct2ReadWrite_Ns = 30;

sdramconfig.tRefreshRecovery_Ns = 70;

sdramconfig.tWriteRecovery_Ns = 4 * ClockCycleNs;

sdramconfig.tCkeOff_Ns = 45;

sdramconfig.tAct2Prechage_Ns = 45;

sdramconfig.tSelfRefRecovery_Ns = 75;

sdramconfig.tRefresh2Refresh_Ns = 50;

sdramconfig.tAct2Act_Ns = 16;

sdramconfig.tIdleTimeout_Ns = 0;

uint32_t TargetNs = RefreshCycleNs / 2;

uint32_t Factor = TargetNs / sdramconfig.tPrescalePeriod_Ns;

Factor = Factor ? Factor : 1;

sdramconfig.refreshPeriod_nsPerRow = Factor * sdramconfig.tPrescalePeriod_Ns;

sdramconfig.refreshUrgThreshold = sdramconfig.refreshPeriod_nsPerRow;

sdramconfig.refreshBurstLen = 1;

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello tom fang,

Sorry for my later reply, I JUST got the powerful reply from our SDRAM expert, please check the following reply:

In fact, the SEMC cannot match the CKE requirement from the AS4C8M16S. The CKE will be pull high when enabling the SEMC and start CLK.

But, the important thing (or the essential point) is, the CKE should be pull high after the CLK being stable. The SEMC can make sure this key point by:

1. Set the CKE PAD with "Pull Down" attribute in SW_PAD_CTL register. (This is the default setting in our SDK) So before enable the SEMC, the CKE PAD will be low.

2. Each time we want to enable the SEMC, the clock root should be set before, so it should be stable when starting the SEMC.

This is why customer's SDRAM can work well even not following the CKE requirement.

So, don't worry, you can use it as what you do right now, it's OK to make your SDRAM work stably.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

--------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

We just only want to meet the requirements of SDRAM datasheet, the SDRAM works good with RT105x and no function problems, but for avoiding any future unpredictable problems, we'd better to meet this requirement.

https://www.alliancememory.com/wp-content/uploads/pdf/dram/128M-AS4C8M16SA.pdf (200us deay, page 20)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tom fang

Thanks for the updated information!

I will help you to check it with our related department, whether there some way to adjust it.

If you still have questions about it, please kindly let us know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you h

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry, any feedback from the "related department"?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tom fang,

Please keep patience, I still wait for the reply, any updated information, will let you know.

Thanks a lot for your understanding.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello tom fang,

Sorry for my later reply, I JUST got the powerful reply from our SDRAM expert, please check the following reply:

In fact, the SEMC cannot match the CKE requirement from the AS4C8M16S. The CKE will be pull high when enabling the SEMC and start CLK.

But, the important thing (or the essential point) is, the CKE should be pull high after the CLK being stable. The SEMC can make sure this key point by:

1. Set the CKE PAD with "Pull Down" attribute in SW_PAD_CTL register. (This is the default setting in our SDK) So before enable the SEMC, the CKE PAD will be low.

2. Each time we want to enable the SEMC, the clock root should be set before, so it should be stable when starting the SEMC.

This is why customer's SDRAM can work well even not following the CKE requirement.

So, don't worry, you can use it as what you do right now, it's OK to make your SDRAM work stably.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

--------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Kerry, I'm glad it's a good news.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, thanks Kerry.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tom fang

Thanks a lot for your understanding, maybe next week I will get the reply, please keep patient, the case already in our internal process!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tom fang ,

I also didn't find the directly control the power on CKE and CLK sequence.

Now, if you didn't give that stable CLK during power, whether your SDRAM works normally or not? Any function problems, or you just want to meet the SDRAM datasheet's demand?

If you still have questions about it, please kindly let us know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------