- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- i.MX RT SEMC DQS Pin; Required or not?

i.MX RT SEMC DQS Pin; Required or not?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX RT SEMC DQS Pin; Required or not?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

In the i.MX RT1050 EVK SDRAM example, the project sets SEMC_DQS pin

IOMUXC_SetPinMux(IOMUXC_GPIO_EMC_39_SEMC_DQS, 1U); /* Software Input On Field: Force input path of pad GPIO_EMC_39 */

IOMUXC_SetPinConfig(

IOMUXC_GPIO_EMC_39_SEMC_DQS, /* GPIO_EMC_39 PAD functional properties : */

0x0110F9u); /* Slew Rate Field: Fast Slew Rate

Drive Strength Field: R0/7

Speed Field: max(200MHz)

Open Drain Enable Field: Open Drain Disabled

Pull / Keep Enable Field: Pull/Keeper Enabled

Pull / Keep Select Field: Keeper

Pull Up / Down Config. Field: 100K Ohm Pull Down

Hyst. Enable Field: Hysteresis Enabled */

But this pin is not connected in the EVK schematic. We are now working on our board and this pin is used for a different purpose. If we configure the pin like above, SDRAM somehow works but we break the other functionality.

It seems "Software Input On Field" is must otherwise the SDRAM does not work. But how a not-connected pin affects the SDRAM? Is there any internal mechanism for the SEMC module for SDRAM? If so, we might consider modifying the board which leaves the pin empty (or connected to the ground like as EVK)

Any idea? Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Murat Cakmak

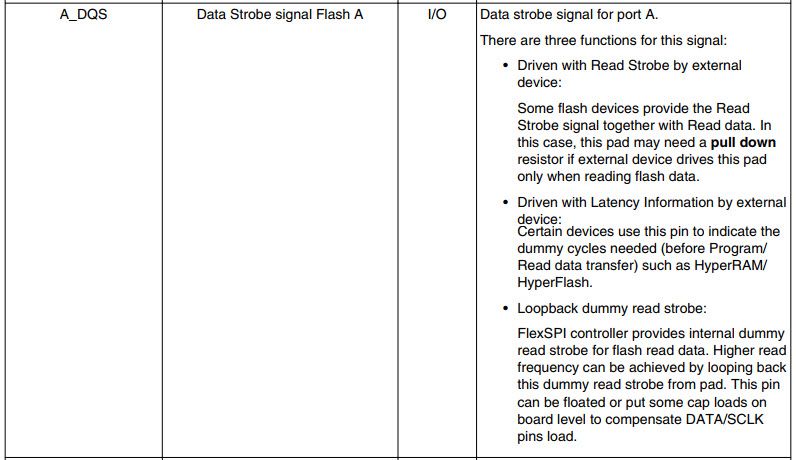

Please see below table from the Reference Manual:

If you going to use the SEMC module, in some cases this pad needs a pull-down resistor, this is why this pin is configured with a pull-down resistor.

Hope this helps

Best regards

Jorge Alcala

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Jorge, just this pins is not connected to External SDRAM, does it still need a pull down resistor?