- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX6ull ethernet problem

iMX6ull ethernet problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, all:

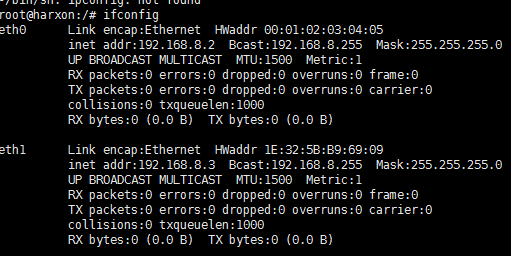

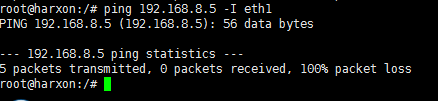

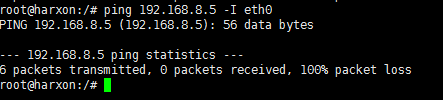

the phy chip for our board is KSZ8081RNBIA1913A3M, now after kernel is loaded, the network is not working.

the host (192.168.8.5) is my pc's address.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, igor.

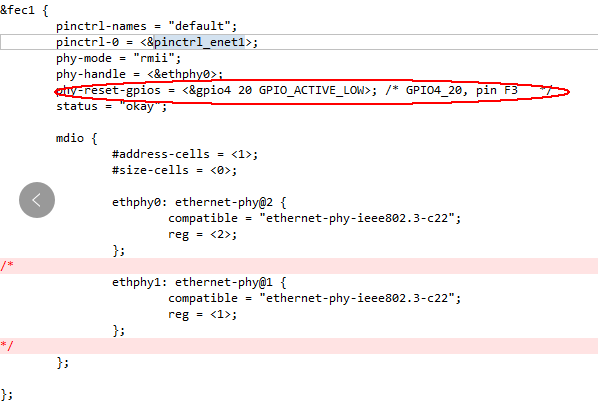

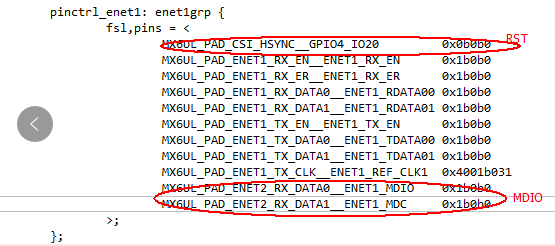

In my boards, We have checked that, our MDIO/MDC pins to change to ENET2_RX_DATA0/1, and RST pin changes to CSI_HSYNC(F3). INT pin keep the same, linked to the SNVS_TAMPER5.

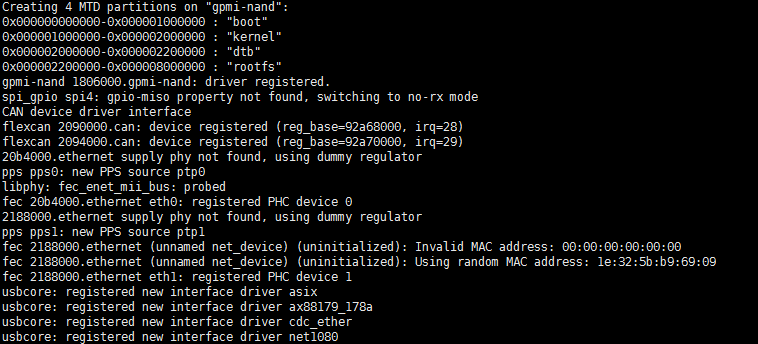

after above changes, we got log like this:

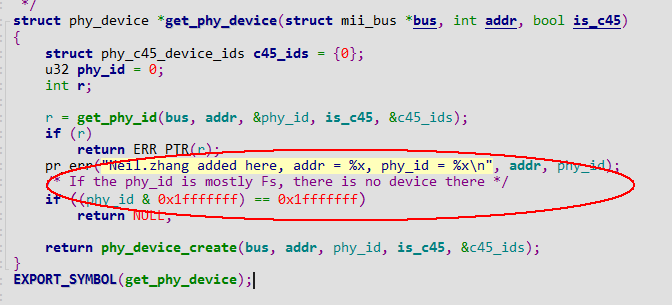

libphy: Neil.zhang added here, addr = 2, phy_id = ffffffff

it seems that the KSZ8081 chip is not working or mdio dts configure err?

edit2:

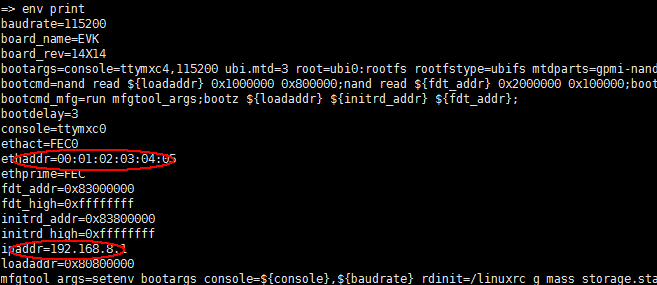

add some info that in uboot env.

Display: TFT43AB (480x272)

Video: 480x272x24

In: serial

Out: serial

Err: serial

Net: FEC0

Error: FEC0 address not set.

Normal Boot

Hit any key to stop autoboot: 0

=> mii info

PHY 0x02: OUI = 0x0885, Model = 0x16, Rev = 0x01, 100baseT, FDX

=> mdio read 0x1

Reading from bus FEC0

PHY at address 0:

1 - 0xffff

=> mdio read 0x2

Reading from bus FEC0

PHY at address 0:

2 - 0xffff

=> mdio read 0x3

Reading from bus FEC0

PHY at address 0:

3 - 0xffff

=> mdio

mdio - MDIO utility commands

Usage:

mdio list - List MDIO buses

mdio read <phydev> [<devad>.]<reg> - read PHY's register at <devad>.<reg>

mdio write <phydev> [<devad>.]<reg> <data> - write PHY's register at <devad>.<reg>

mdio rx <phydev> [<devad>.]<reg> - read PHY's extended register at <devad>.<reg>

mdio wx <phydev> [<devad>.]<reg> <data> - write PHY's extended register at <devad>.<reg>

<phydev> may be:

<busname> <addr>

<addr>

<eth name>

<addr> <devad>, and <reg> may be ranges, e.g. 1-5.4-0x1f.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 国承 张

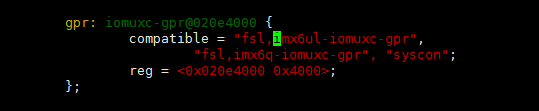

one can check enet clock with oscilloscope and debug it in function

setup_fec(int fec_id) paying attention to clock direction set by IOMUX_GPR1

mx6ullevk.c\mx6ullevk\freescale\board - uboot-imx - i.MX U-Boot

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks igor.

our baseline is L4.1.15

on my board, I have check that ENET1_TX_CLK is 50Mhz, and ENET1_nRST is low.

and in the file uboot/include/configs/imx6ullevk.h, I have change the CONFIG_FEC_ENET_DEV from 1 to 0. because on my board, there is only one phy for ENET1.

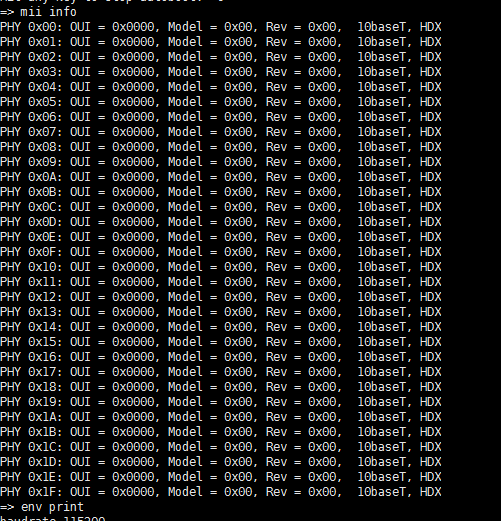

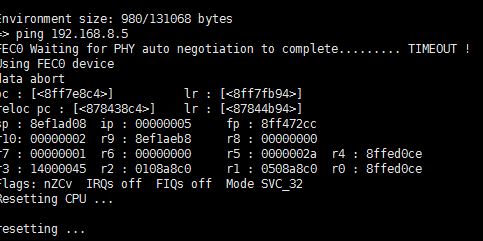

and after set env in uboot, this is no mii info on my board.

and when I ping the host connected my board, the uboot reset...

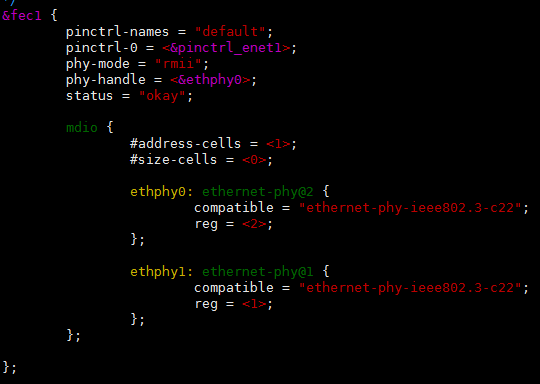

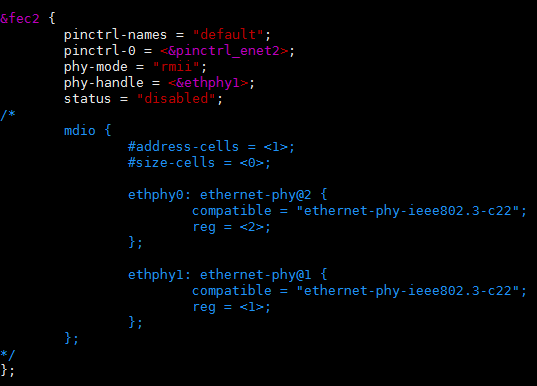

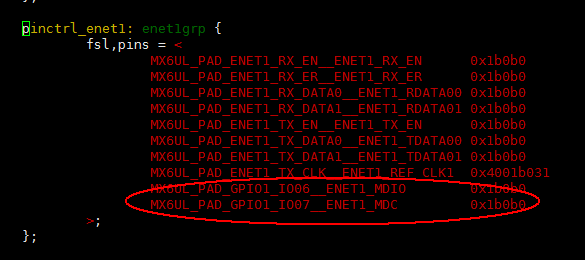

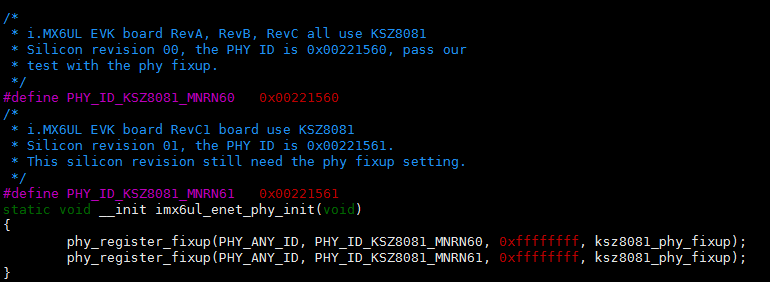

in kernel. I have do some follow changes:

and the left led of the RJ45 port is off status.

is there any other suggestions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so had you checked enet clock with oscilloscope, is it present?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, igor.

In my boards, We have checked that, our MDIO/MDC pins to change to ENET2_RX_DATA0/1, and RST pin changes to CSI_HSYNC(F3). INT pin keep the same, linked to the SNVS_TAMPER5.

after above changes, we got log like this:

libphy: Neil.zhang added here, addr = 2, phy_id = ffffffff

it seems that the KSZ8081 chip is not working or mdio dts configure err?

edit2:

add some info that in uboot env.

Display: TFT43AB (480x272)

Video: 480x272x24

In: serial

Out: serial

Err: serial

Net: FEC0

Error: FEC0 address not set.

Normal Boot

Hit any key to stop autoboot: 0

=> mii info

PHY 0x02: OUI = 0x0885, Model = 0x16, Rev = 0x01, 100baseT, FDX

=> mdio read 0x1

Reading from bus FEC0

PHY at address 0:

1 - 0xffff

=> mdio read 0x2

Reading from bus FEC0

PHY at address 0:

2 - 0xffff

=> mdio read 0x3

Reading from bus FEC0

PHY at address 0:

3 - 0xffff

=> mdio

mdio - MDIO utility commands

Usage:

mdio list - List MDIO buses

mdio read <phydev> [<devad>.]<reg> - read PHY's register at <devad>.<reg>

mdio write <phydev> [<devad>.]<reg> <data> - write PHY's register at <devad>.<reg>

mdio rx <phydev> [<devad>.]<reg> - read PHY's extended register at <devad>.<reg>

mdio wx <phydev> [<devad>.]<reg> <data> - write PHY's extended register at <devad>.<reg>

<phydev> may be:

<busname> <addr>

<addr>

<eth name>

<addr> <devad>, and <reg> may be ranges, e.g. 1-5.4-0x1f.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes, I have checked.

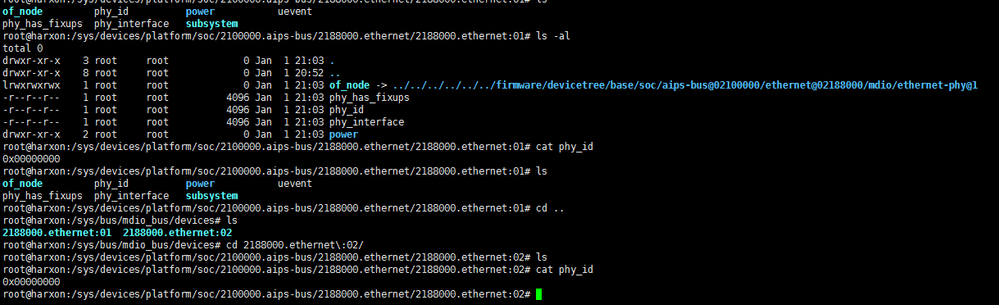

I have add some log in my baseline L4.1.15, found that phydev->phy_id is zero, does this means the phy chip is not work ?

fec 2188000.ethernet (unnamed net_device) (uninitialized): Invalid MAC address: 00:00:00:00:00:00

fec 2188000.ethernet (unnamed net_device) (uninitialized): Using random MAC address: 66:14:2a:50:c3:1a

Neil.zhang added here, before of_mdiobus_register

libphy: Neil.zhang added here, mido_register begin...

libphy: fec_enet_mii_bus: probed

libphy: Neil.zhang added here, phy_device_register

libphy: Neil.zhang added here, phy_scan_fixups

libphy: Neil.zhang added here, phy_uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_id is 0, uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_needs_fixup ret false, phy_uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_uid = 221561, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_id is 0, uid = 221561, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_needs_fixup ret false, phy_uid = 221561, uid_mask = ffffffff

Neil.zhang added here, phy_device_register ret zero

mdio_bus 2188000.ethernet: registered phy ethernet-phy at address 2

libphy: Neil.zhang added here, phy_device_register

libphy: Neil.zhang added here, phy_scan_fixups

libphy: Neil.zhang added here, phy_uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_id is 0, uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_needs_fixup ret false, phy_uid = 221560, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_uid = 221561, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_id is 0, uid = 221561, uid_mask = ffffffff

libphy: Neil.zhang added here, phy_needs_fixup ret false, phy_uid = 221561, uid_mask = ffffffff

Neil.zhang added here, phy_device_register ret zero

mdio_bus 2188000.ethernet: registered phy ethernet-phy at address 1

another question ? what about you mean that check IOMUXC_GPR, I have no idea about that.

for full dmesg log, please refer to attachment.

edit 2st: