- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- FOPT kw41z irq on reset_b

FOPT kw41z irq on reset_b

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FOPT kw41z irq on reset_b

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

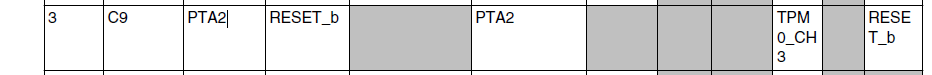

i 'm trying to enable interrupt on PTA2 of kw41z.

I write in FOPT register (datasheet table 6.2) the value F7.

Have you any suggests?

Tnx

G.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The reason is because the hardware was done with the configuration above reported and at the moment i cannot change it.

I reprogram device by running program flash as soon as i connect mcu to power source.

Regards,

Gaetano

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

So you do not have a way to debug it ? Are you using the freedom board?

Regards,

Estephania

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, i'm using a custom hardware with mk41z chipset.

I can debig with print, the swd port are used as spi.

Regards

Gaetano

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

It is hardly impossible to perform a memory dump with your current setup and I'm not sure if the problem it's regarding configuration of the pin, the hardware design and the way you have it configured we can't really know what it's happening in code as you do not have a way to debug it.

Have you tested this before in one of our developments boards? Also, what did you do with the NMI pin in both hardware and software? Do you have a way to test it using another pin that it's not the A2?

Regards,

Estephania

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Others info:

I'm using IAR and i have enabled loader option:

--enable_config_write

After setting FOPT register, on startup, i set the PTA2 as input gpio.

The program execute until one of the exception pin appears on IRQ pin (PTA2).

The program seems to hold in reset state.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

If you check the reference manual of the device you are using you can confirm that this pins does not have the GPIO functionality and this it's the reset pin of the device.

Are you sure that you are configuring the correct MUX functionality ? Also, are you sure you want to set it that way ? What are you trying to do?

You will need to check as well the 6.2.2.2 Low-voltage detect (LVD) chapter of the manual.

Hope it helps!

Regards,

Estephania

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I' m trying to execute irq handler on falling edge of PTA2. My hardware project have 2 components (sc16is7x and atwinc ) with irq pin connected to PTA2. I want execute their interrupt handler on IRQ low of their interrupt pin. So i need to configure this pin to execute proprietary interrupt handler and not resetting the chip.

The gpio is configured correctly as alt1.

The behaviour is that the chip qhen interrupt occurr remains halted/freezed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

But is there a specific reason why you want to use that pin ? Why not using another pin as the interrupt one? Why does it have to be the reset one?

The behavior you seem to be having would appear to be a fault or an assert, are you able to reprogram your device? How are you resetting your device to reprogram it ?

Regards,

Estephania