- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Sensors

- :

- Speed up SPI KV58

Speed up SPI KV58

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using a Tower KV58 Demo board trying to talk to a AD5601 SPI 16-bit DAC

I have been able to talk to the DAC fine using the attached program. It has a 24 Bit transfer with the first 8 bits 0's and the other 16 bits the data bits.

What I'm seeing as 1.2 us of DAC transfer and then 7.3 us of delay., for a total of about 8.5 us between DAC writes. The DAC can take data with only a 1 us delay. I need to get the current 7.3 us delay down to less than 4 us. I don't need a SPI read since the data is useless after 4 us, so just move on to the next write.

I tried increasing the TRANSFER_BAUDRATE to 32000000 but that didn't work with the TOWER KV58. I thought this would have solved the problem.

Possibly I'm not using the right technology for this (Master Half Duplex DMA). I have tried some other Tower Board examples but this is the best I've gotten so far.

Any suggestions would be greatly appreciated.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken,

Have you checked the Delay after Transfer Prescaler?

This register can be used to decrease the delay between transfers and you can modify it using the SDK.

masterConfig->ctarConfig.betweenTransferDelayInNanoSec

Hope it helps!

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken,

Have you checked the Delay after Transfer Prescaler?

This register can be used to decrease the delay between transfers and you can modify it using the SDK.

masterConfig->ctarConfig.betweenTransferDelayInNanoSec

Hope it helps!

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Felipe,

Thank you.

I did see that setting but I changed it to 0, which seemed to be allowed, and it had no effect on the between transfer time. Before that it was 1000000000U / TRANSFER_BAUDRATE; AND TRANSFER_BAUDRATE was 16000000 so 62.5.

Essentially I did get the program working but I'm a little unsure why it is working. I incorporated it into my program which works on interrupts. Possibly the way I have interrupts setup in my program was somehow compatible with the way the SPI program wanted the interrupts setup and they work together. Thanks for all your help.

Ken

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

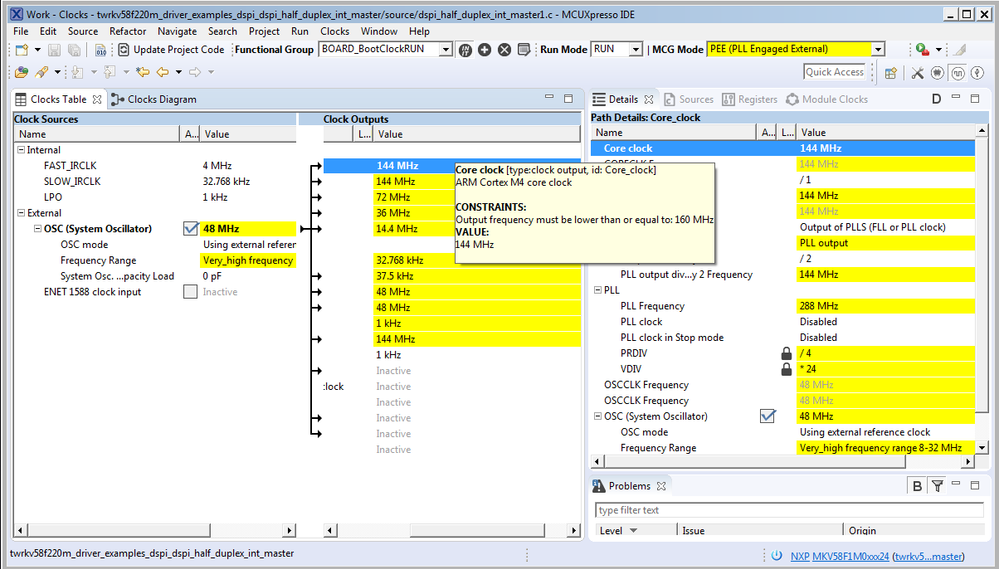

I tried to change the clock but nothing happened. I was seeing 240MHz for the System clock on the Clock configuration tab with HSRun but the timing on the system didn't change. Is there documentation on setting up the clocks that I have not found? Can someone point me to documentation or explain to me how the Run mode is different than the Functional Group? My Functional Group is BOARD_BootClockHSRUN and my Run mode is HSRUN. I'm not sure I'm actually using that mode.

I finally realized that I need to use the:

BOARD_BootClockHSRUN();

vs

//BOARD_BootClockRUN();

to initialize the clocks. Possibly I still don't have the right clocks or Clock startup function. This helped but still didn't significantly change the delay timing between SPI data send.. It seemed to cut the 1.2 us send to about 1.1us, or I'm just making finer measurements now. It did not significantly change the delay between sends. I'm still not getting the timing I need. Any other thought would be greatly appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ken,

What is your CPU clock? TWR-KV58 can run up to 240 MHz. I'd recommend you to increase the system clock frequency and see if it works.

You can change the clock using MCUXpresso Config Tools.

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Felipe,

Thank you for the advice. I saw the documentation that said the board could do that, but I've been unable to find a way to change the clock to that speed. Attached is my current clock configuration. Any help or advice you can provide to help me figure out what to set, or how to speed it up would be greatly appreciated.

Thanks

Ken

EDITED: I did find, just now, that if I changed to the HSRUN, I could find a way to get the processor to go up to 240 MHz but I see the SPI0 (Fast Peripheral Clock) clock is still a maximum of 144MHz. Which seems to be double the 72 MHz that I'm using now. I'll try that to see what it changes but if you have any other ideas I'm open to hearing them.

Thanks for getting me to look at it again. I'm not sure why I didn't see that before.

Ken