- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Request Some Help with Flash Block on MC9S12E128

Request Some Help with Flash Block on MC9S12E128

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Request Some Help with Flash Block on MC9S12E128

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

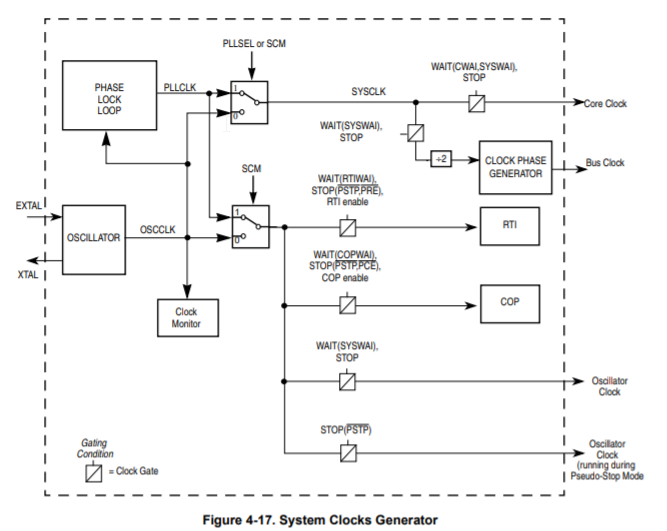

I'm a bit confused about the clocks that are referenced in the FTS128K1. I'm running the uP on a 16Mhz crystal and I believe that means my oscillator clock is 16MHz and my BUS clock is 8MHz per this diagram. Please confirm.

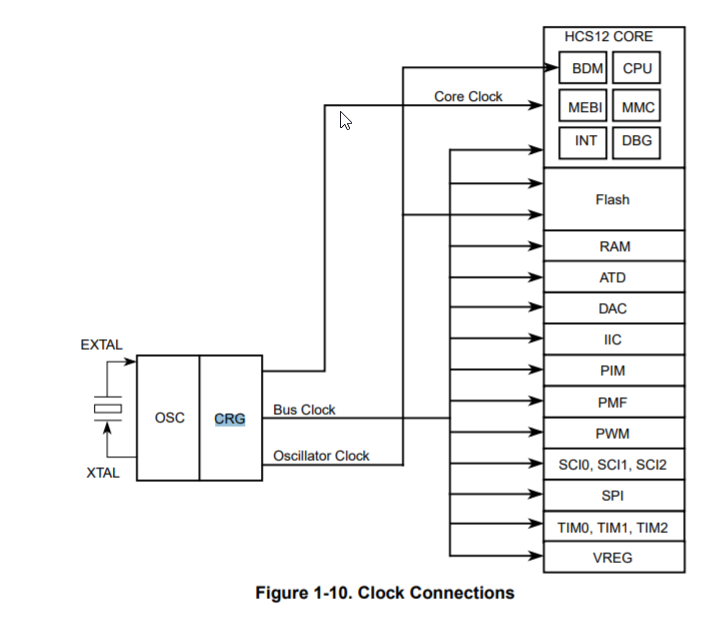

Also, this diagram shows both clocks go to the flash module...

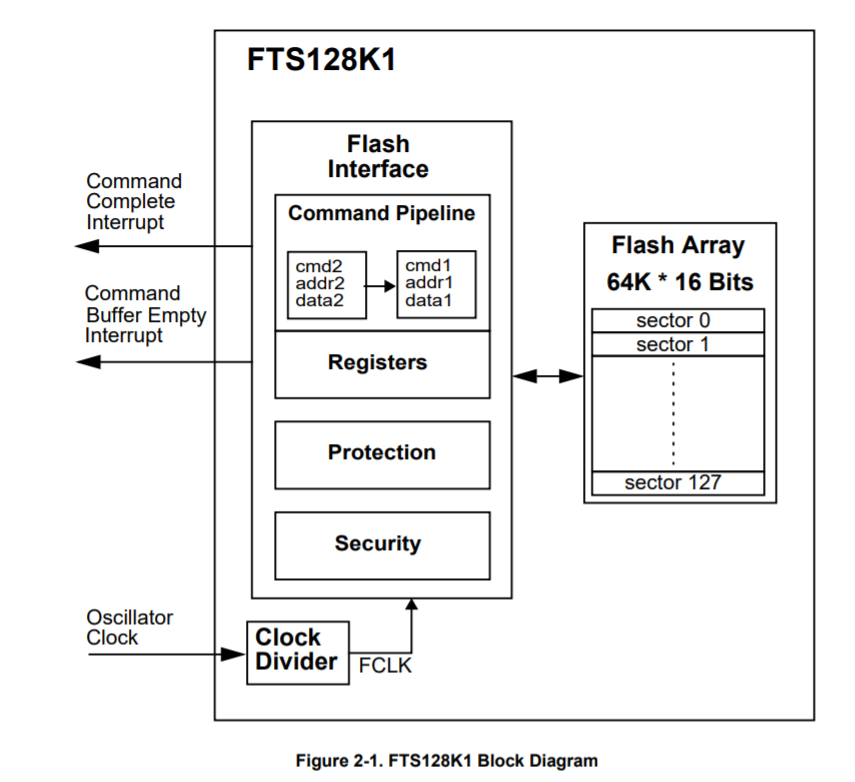

But this diagram suggests only the oscillator clock goes to the flash module...

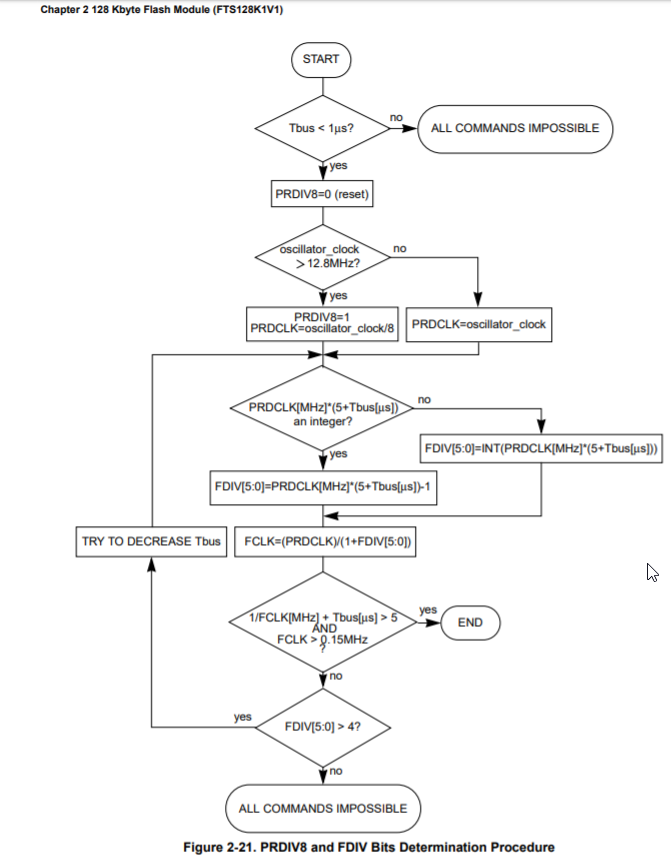

So here is the diagram where I need confirmation that oscillator clock is indeed the 16Mhz in my configuration and Tbus related to the 8MHz BUS clock:

Thanks,

-Rich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

if you do not use PLL then BUSCLK is OSCCLK/2. 16MHz OSCCLK => 8MHz BUSCLK.

The OSCCLK is a source clock for Flash. (But BUSCLK also appears in the FCLKDIV calculation)

In the far past I created an excel which calculates the FCLKDIV value and it is attached.

If you use above mentioned values then FCLKDIV = 74; // FCLKDIV = 0x4A;

Moreover, I have attached an example for Flash E/W. It is made under CodeWarrior v. 4.7. ..Also historical thing, yr. 2008.

Finaly, I use the calculation routine for FCLKDIV value in the attached example as a part of the code. It is up to you which one is better for you.

Best regards,

Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Very helpful. Thank you. Please confirm that Tbus is actually, 1/2 of the period. In the code example you show for an 11.0592MHz oscillator clock Tbus is 90ns (not 180ns like the period would be for bus clock).

Thanks,

-Rich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually spreadsheet suggest Tbus is the BUS clock period but code sample used 1/2 of the period. Please confirm the spreadsheet is correct.

Thanks,

-Rich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are right, there are two mistakes (copy/paste, tests I made in history solving different issues,...)

the code I store in my PC is code I used for tests of different values and there are a few old info. Everything looks to be good except a few lines:

Original:

// ucx = Flash_Init(11059,90); // Oscillator clock is 11059 kHz, bus clock is 5.5296MHz => tbus=90ns

// or this function

FCLKDIV = 57;

(void)Flash_CatchError(ucx,1); // function used only for debugging purposes

// ucx = Flash_Init(16000,125); // Oscillator clock is 16000 kHz, bus clock is 8MHz => tbus=125ns

// ucx = Flash_Init(8000,250); // Oscillator clock is 8000 kHz, bus clock is 4MHz => tbus=250ns

// ucx = Flash_Init(5000,125); // Oscillator clock is 5000 kHz, bus clock is 8MHz => tbus=125ns

// ucx = Flash_Init(4000,500); // Oscillator clock is 4000 kHz, bus clock is 2MHz => tbus=500ns

Corrected values:

// ucx = Flash_Init(11059,180); // Oscillator clock is 11059 kHz, bus clock is 5.5296MHz => tbus=180ns

// or this function

FCLKDIV = 57; // absolutely correct for fosc 11059200Hz OSCCLK and 5529600 BUSCLK

(void)Flash_CatchError(ucx,1); // function used only for debugging purposes

// ucx = Flash_Init(16000,125); // Oscillator clock is 16000 kHz, bus clock is 8MHz => tbus=125ns

// ucx = Flash_Init(8000,250); // Oscillator clock is 8000 kHz, bus clock is 4MHz => tbus=250ns

// ucx = Flash_Init(5000,400); // Oscillator clock is 5000 kHz, bus clock is 8MHz => tbus=400ns

// ucx = Flash_Init(4000,500); // Oscillator clock is 4000 kHz, bus clock is 2MHz => tbus=500ns

fbus = OSCCLK/2 or PLLCLK/2 if PLL is used.

Tbus = 1 / fbus

OSCCLK is used as a source clock for flash.

Note. In the excel calculator BUSCLK do not have t be OSCCLK/2 because if you use PLL then BUSCLK=PLLCLK/2.

Best regards,

Ladislav