- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Restriction of Fractional Delay Circuit in KV5x to work

Restriction of Fractional Delay Circuit in KV5x to work

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Restriction of Fractional Delay Circuit in KV5x to work

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

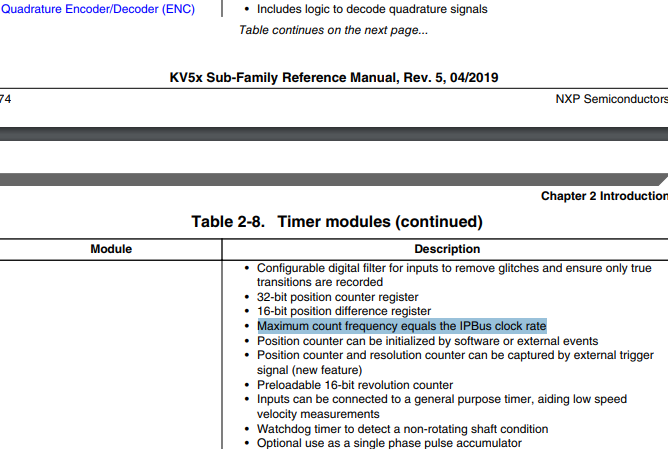

Document KV5X sub-family reference manual describes

a) "The fractional delay logic can only be used when the IPBus clock is running at 100 MHz."

in FRAC_PU bit description of PWMx_SMnFRCTRL field.

b) "Using the micro-edge placer block requires that the Fast-Peripheral clock be set within a

valid frequency range (see the data sheet of this device for minimum and maximum

values) and the core/system clock must be programmed to be 2x the Fast Peripheral

clock." in 48.5.2.9.1 Fractional Delay Logic with Nano-Edge Placement Block

For above b), data sheet indicates 120MHz as max value of Fast-Peripheral clock.

If Fast-Peripheral clock is set to 120MHz, fractional delay logic will not work by reason a) ?

Please help how I understand this conflict of restriction.

BR.

Masato Nishimoto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear seapon@seapons.com,

Check the following description for IPBus:

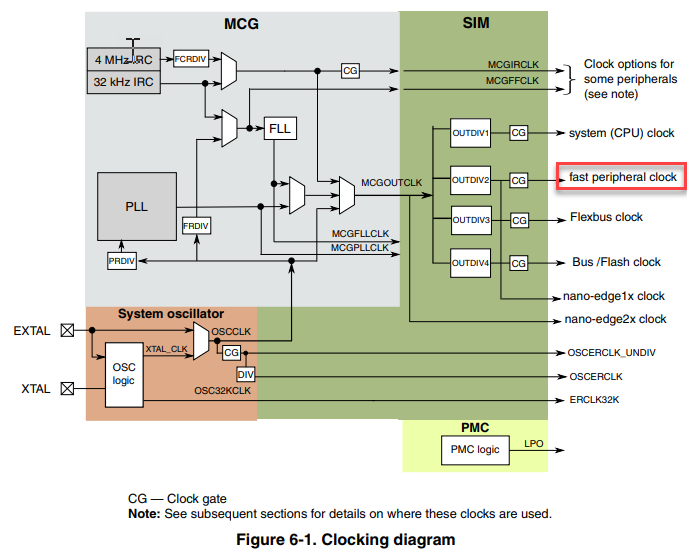

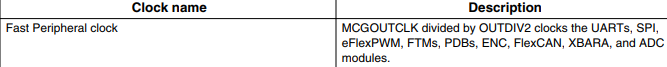

The Fast Peripheral Clock is part of the clock distribution and set in the MCG:

So if you'll need to set both clock to the respective ranges.

I hope this helps you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alexis,

Than you for your mail.

To use the micro-edge placer block, we use MCGOUTCLK (=240MHz) and fast peripheral clock (=120MHz).

However, FRAC_PU bit description of PWMx_SMnFRCTRL field mentions "The fractional delay logic can only be used when

the IPBus clock is running at 100 MHz.".

What is relation between Fractional delay logic and IPBus clock?

Where is IPBus clock comes from (I cannot find IPBus clock at clocking diagram)?

How I can control frequency of IPBus clock?

Please let me know above.

Best Regards,

Masato Nishimoto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear seapon@seapons.com,

Sorry but I made a mistake about this, the only clock that supply the PWM is the Fast Peripheral Clock.

So you'll need to set the core clock at 200 MHz if you want fractional delay logic.

I'm sorry for this mistake.

Best Regards,

Alexis Andalon