- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- No IVOR1 exception even after ERM module reports errors

No IVOR1 exception even after ERM module reports errors

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

No IVOR1 exception even after ERM module reports errors

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I am trying to inject an error via EIM and detect via ERM as per example. the example is working as expected but when in do the same thing in my code my ERM is detecting the error but is not able to invoke IVOR1 handler.

link to example https://community.nxp.com/docs/DOC-328097

when i execute it my ERM reports that the error is injected but the function Machine_check_handler() is not being invoked by IVOR1 WHY?

I am using the same assembly files given in the above example for startup and interrupt initialization

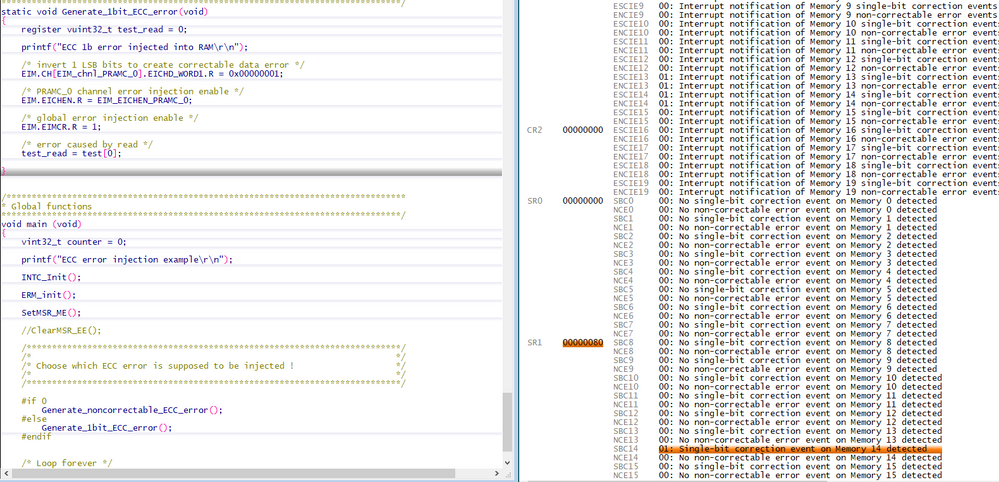

Debugger O/P

BEFORE

/** Cause an error by read operation */

test_read = test[0];

Core Registers

R0 0083DB98 R8 1 R16 0 R24 4004185A ^S+ ^Stack_+

R1 40080F30 R9 8A R17 0 R25 00857138

R2 0085F0B4 R10 0 R18 0 R26 0085712C

R3 02009000 R11 00856FF0 R19 0 R27 00857138

R4 1000 R12 1 R20 0 R28 40080FB0

R5 FFE6422C R13 40048000 R21 0 R29 40080F5C

R6 FFF64000 R14 0 R22 0 R30 40080F64

R7 1 R15 0 R23 0 R31 1

--------------------------------------------------------------

TBL EFB993C2 XER 0 CR 20000000 LR 0083DB98

TBU F0D20C0C USPRG03F8F507F CTR 4004189E IP 0083DF38

--------------------------------------------------------------

SPRG0 BD8EFB97 SRR0 00853360 IVPR 00850000 MSR 02008000

SPRG1 590CEEFB SRR1 1000 DEAR 158E0418 PVR 816A0000

SPRG2 641FABE7 CSRR0 6E9B5AB6 ESR 0 DEC 0BABEAFE

SPRG3 E3EB176A CSRR1 C43E7793 MCSR 0 DECAR DC6A1668

SPRG4 B14F767B MCSRR075FE2A71 MCAR 000CF001 TCR 0

SPRG5 CB65DC71 MCSRR1740EFDBF TSR 0

SPRG6 E94FF9FD PID 0

SPRG7 F8A9D1F6

SPRG8 8DCEC43D UCLE _ SPE S WE _ CE _ EE E PR _

SPRG9 EFD7A7BF FP _ ME _ DE _ IS _ DS _ RI _

EIM - Error Injection Module

EIMCR 00000001 GEIEN 01: Enabled

EICHEN 40000000 EICH0EN 00: Error injection is disabled on Error Injection Channel 0

EICH1EN 01: Error injection is enabled on Error Injection Channel 1

EICH2EN 00: Error injection is disabled on Error Injection Channel 2

EICH3EN 00: Error injection is disabled on Error Injection Channel 3

EICH4EN 00: Error injection is disabled on Error Injection Channel 4

EICH5EN 00: Error injection is disabled on Error Injection Channel 5

EICHD0_WORD0 00000000 CHKBIT_MASK 00

EICHD0_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD0_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD1_WORD0 00000000 CHKBIT_MASK 00

EICHD1_WORD1 00000001 B0_3DATA_MASK 00000001

EICHD1_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD2_WORD0 00000000 CHKBIT_MASK 00

EICHD2_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD2_WORD2 ???????? B4_7DATA_MASK

EICHD3_WORD0 00000000 CHKBIT_MASK 00

EICHD3_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD3_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD4_WORD0 00000000 CHKBIT_MASK 00

EICHD4_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD4_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD5_WORD0 00000000 CHKBIT_MASK 00

EICHD5_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD5_WORD2 00000000 B4_7DATA_MASK 00000000

eMIOS - Configurable Enhanced Modular IO Subsystems

EQADC - Enhanced Queued Analog-to-Digital Converters

ERM - Error Reporting Module

CR0 00000000 ESCIE0 00: Interrupt notification of Memory 0 single-bit correction events is disabled

ENCIE0 00: Interrupt notification of Memory 0 non-correctable error events is disabled

ESCIE1 00: Interrupt notification of Memory 1 single-bit correction events is disabled

ENCIE1 00: Interrupt notification of Memory 1 non-correctable error events is disabled

ESCIE2 00: Interrupt notification of Memory 2 single-bit correction events is disabled

ENCIE2 00: Interrupt notification of Memory 2 non-correctable error events is disabled

ESCIE3 00: Interrupt notification of Memory 3 single-bit correction events is disabled

ENCIE3 00: Interrupt notification of Memory 3 non-correctable error events is disabled

ESCIE4 00: Interrupt notification of Memory 4 single-bit correction events is disabled

ENCIE4 00: Interrupt notification of Memory 4 non-correctable error events is disabled

ESCIE5 00: Interrupt notification of Memory 5 single-bit correction events is disabled

ENCIE5 00: Interrupt notification of Memory 5 non-correctable error events is disabled

ESCIE6 00: Interrupt notification of Memory 6 single-bit correction events is disabled

ENCIE6 00: Interrupt notification of Memory 6 non-correctable error events is disabled

ESCIE7 00: Interrupt notification of Memory 7 single-bit correction events is disabled

ENCIE7 00: Interrupt notification of Memory 7 non-correctable error events is disabled

CR1 00000000 ESCIE8 00: Interrupt notification of Memory 8 single-bit correction events is disabled

ENCIE8 00: Interrupt notification of Memory 8 non-correctable error events is disabled

ESCIE9 00: Interrupt notification of Memory 9 single-bit correction events is disabled

ENCIE9 00: Interrupt notification of Memory 9 non-correctable error events is disabled

ESCIE10 00: Interrupt notification of Memory 10 single-bit correction events is disabled

ENCIE10 00: Interrupt notification of Memory 10 non-correctable error events is disabled

ESCIE11 00: Interrupt notification of Memory 11 single-bit correction events is disabled

ENCIE11 00: Interrupt notification of Memory 11 non-correctable error events is disabled

ESCIE12 00: Interrupt notification of Memory 12 single-bit correction events is disabled

ENCIE12 00: Interrupt notification of Memory 12 non-correctable error events is disabled

ESCIE13 00: Interrupt notification of Memory 13 single-bit correction events is disabled

ENCIE13 00: Interrupt notification of Memory 13 non-correctable error events is disabled

ESCIE14 00: Interrupt notification of Memory 14 single-bit correction events is disabled

ENCIE14 00: Interrupt notification of Memory 14 non-correctable error events is disabled

ESCIE15 00: Interrupt notification of Memory 15 single-bit correction events is disabled

ENCIE15 00: Interrupt notification of Memory 15 non-correctable error events is disabled

CR2 00000000 ESCIE16 00: Interrupt notification of Memory 16 single-bit correction events is disabled

ENCIE16 00: Interrupt notification of Memory 16 non-correctable error events is disabled

ESCIE17 00: Interrupt notification of Memory 17 single-bit correction events is disabled

ENCIE17 00: Interrupt notification of Memory 17 non-correctable error events is disabled

ESCIE18 00: Interrupt notification of Memory 18 single-bit correction events is disabled

ENCIE18 00: Interrupt notification of Memory 18 non-correctable error events is disabled

ESCIE19 00: Interrupt notification of Memory 19 single-bit correction events is disabled

ENCIE19 00: Interrupt notification of Memory 19 non-correctable error events is disabled

SR0 00000000 SBC0 00: No single-bit correction event on Memory 0 detected

NCE0 00: No non-correctable error event on Memory 0 detected

SBC1 00: No single-bit correction event on Memory 1 detected

NCE1 00: No non-correctable error event on Memory 1 detected

SBC2 00: No single-bit correction event on Memory 2 detected

NCE2 00: No non-correctable error event on Memory 2 detected

SBC3 00: No single-bit correction event on Memory 3 detected

NCE3 00: No non-correctable error event on Memory 3 detected

SBC4 00: No single-bit correction event on Memory 4 detected

NCE4 00: No non-correctable error event on Memory 4 detected

SBC5 00: No single-bit correction event on Memory 5 detected

NCE5 00: No non-correctable error event on Memory 5 detected

SBC6 00: No single-bit correction event on Memory 6 detected

NCE6 00: No non-correctable error event on Memory 6 detected

SBC7 00: No single-bit correction event on Memory 7 detected

NCE7 00: No non-correctable error event on Memory 7 detected

SR1 00000000 SBC8 00: No single-bit correction event on Memory 8 detected

NCE8 00: No non-correctable error event on Memory 8 detected

SBC9 00: No single-bit correction event on Memory 9 detected

NCE9 00: No non-correctable error event on Memory 9 detected

SBC10 00: No single-bit correction event on Memory 10 detected

NCE10 00: No non-correctable error event on Memory 10 detected

SBC11 00: No single-bit correction event on Memory 11 detected

NCE11 00: No non-correctable error event on Memory 11 detected

SBC12 00: No single-bit correction event on Memory 12 detected

NCE12 00: No non-correctable error event on Memory 12 detected

SBC13 00: No single-bit correction event on Memory 13 detected

NCE13 00: No non-correctable error event on Memory 13 detected

SBC14 00: No single-bit correction event on Memory 14 detected

NCE14 00: No non-correctable error event on Memory 14 detected

SBC15 00: No single-bit correction event on Memory 15 detected

NCE15 00: No non-correctable error event on Memory 15 detected

SR2 00000000 SBC16 00: No single-bit correction event on Memory 16 detected

NCE16 00: No non-correctable error event on Memory 16 detected

SBC17 00: No single-bit correction event on Memory 17 detected

NCE17 00: No non-correctable error event on Memory 17 detected

SBC18 00: No single-bit correction event on Memory 18 detected

NCE18 00: No non-correctable error event on Memory 18 detected

SBC19 00: No single-bit correction event on Memory 19 detected

NCE19 00: No non-correctable error event on Memory 19 detected

EAR0 00000000 EAR 00000000

SYN0 00000000 SYNDROME 00

EAR1 00000000 EAR 00000000

SYN1 00000000 SYNDROME 00

EAR2 00000000 EAR 00000000

SYN2 00000000 SYNDROME 00

EAR3 00000000 EAR 00000000

SYN3 00000000 SYNDROME 00

EAR4 00000000 EAR 00000000

SYN4 00000000 SYNDROME 00

EAR5 00000000 EAR 00000000

SYN5 00000000 SYNDROME 00

EAR6 00000000 EAR 00000000

SYN6 00000000 SYNDROME 00

EAR7 00000000 EAR 00000000

SYN7 00000000 SYNDROME 00

EAR8 00000000 EAR 00000000

SYN8 00000000 SYNDROME 00

EAR9 00000000 EAR 00000000

SYN9 00000000 SYNDROME 00

EAR10 00000000 EAR 00000000

SYN10 00000000 SYNDROME 00

EAR11 00000000 EAR 00000000

SYN11 00000000 SYNDROME 00

EAR12 00000000 EAR 00000000

SYN12 00000000 SYNDROME 00

EAR13 00000000 EAR 00000000

SYN13 00000000 SYNDROME 00

EAR14 00000000 EAR 00000000

SYN14 00000000 SYNDROME 00

EAR15 00000000 EAR 00000000

SYN15 00000000 SYNDROME 00

EAR16 00000000 EAR 00000000

SYN16 00000000 SYNDROME 00

EAR17 00000000 EAR 00000000

SYN17 00000000 SYNDROME 00

EAR18 00000000 EAR 00000000

SYN18 00000000 SYNDROME 00

EAR19 00000000 EAR 00000000

SYN19 00000000 SYNDROME 00

AFTER

/** Cause an error by read operation */

test_read = test[0];

Core Registers

R0 0083DB98 R8 1 R16 0 R24 4004185A ^S+ ^Stack_+

R1 40080F30 R9 8A R17 0 R25 00857138

R2 0085F0B4 R10 0 R18 0 R26 0085712C

R3 02009000 R11 00856FF0 R19 0 R27 00857138

R4 1000 R12 1 R20 0 R28 40080FB0

R5 FFE6422C R13 40048000 R21 0 R29 40080F5C

R6 FFF64000 R14 0 R22 0 R30 40080F64

R7 11111111 R15 0 R23 0 R31 1

--------------------------------------------------------------

TBL EFB993C2 XER 0 CR 20000000 LR 0083DB98

TBU F0D20C0C USPRG03F8F507F CTR 4004189E IP 0083DF40

--------------------------------------------------------------

SPRG0 BD8EFB97 SRR0 00853360 IVPR 00850000 MSR 02008000

SPRG1 590CEEFB SRR1 1000 DEAR 158E0418 PVR 816A0000

SPRG2 641FABE7 CSRR0 6E9B5AB6 ESR 0 DEC 0BABEAFE

SPRG3 E3EB176A CSRR1 C43E7793 MCSR 0 DECAR DC6A1668

SPRG4 B14F767B MCSRR075FE2A71 MCAR 000CF001 TCR 0

SPRG5 CB65DC71 MCSRR1740EFDBF TSR 0

SPRG6 E94FF9FD PID 0

SPRG7 F8A9D1F6

SPRG8 8DCEC43D UCLE _ SPE S WE _ CE _ EE E PR _

SPRG9 EFD7A7BF FP _ ME _ DE _ IS _ DS _ RI _

EIM - Error Injection Module

EIMCR 00000001 GEIEN 01: Enabled

EICHEN 40000000 EICH0EN 00: Error injection is disabled on Error Injection Channel 0

EICH1EN 01: Error injection is enabled on Error Injection Channel 1

EICH2EN 00: Error injection is disabled on Error Injection Channel 2

EICH3EN 00: Error injection is disabled on Error Injection Channel 3

EICH4EN 00: Error injection is disabled on Error Injection Channel 4

EICH5EN 00: Error injection is disabled on Error Injection Channel 5

EICHD0_WORD0 00000000 CHKBIT_MASK 00

EICHD0_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD0_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD1_WORD0 00000000 CHKBIT_MASK 00

EICHD1_WORD1 00000001 B0_3DATA_MASK 00000001

EICHD1_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD2_WORD0 00000000 CHKBIT_MASK 00

EICHD2_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD2_WORD2 ???????? B4_7DATA_MASK

EICHD3_WORD0 00000000 CHKBIT_MASK 00

EICHD3_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD3_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD4_WORD0 00000000 CHKBIT_MASK 00

EICHD4_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD4_WORD2 00000000 B4_7DATA_MASK 00000000

EICHD5_WORD0 00000000 CHKBIT_MASK 00

EICHD5_WORD1 00000000 B0_3DATA_MASK 00000000

EICHD5_WORD2 00000000 B4_7DATA_MASK 00000000

eMIOS - Configurable Enhanced Modular IO Subsystems

EQADC - Enhanced Queued Analog-to-Digital Converters

ERM - Error Reporting Module

CR0 00000000 ESCIE0 00: Interrupt notification of Memory 0 single-bit correction events is disabled

ENCIE0 00: Interrupt notification of Memory 0 non-correctable error events is disabled

ESCIE1 00: Interrupt notification of Memory 1 single-bit correction events is disabled

ENCIE1 00: Interrupt notification of Memory 1 non-correctable error events is disabled

ESCIE2 00: Interrupt notification of Memory 2 single-bit correction events is disabled

ENCIE2 00: Interrupt notification of Memory 2 non-correctable error events is disabled

ESCIE3 00: Interrupt notification of Memory 3 single-bit correction events is disabled

ENCIE3 00: Interrupt notification of Memory 3 non-correctable error events is disabled

ESCIE4 00: Interrupt notification of Memory 4 single-bit correction events is disabled

ENCIE4 00: Interrupt notification of Memory 4 non-correctable error events is disabled

ESCIE5 00: Interrupt notification of Memory 5 single-bit correction events is disabled

ENCIE5 00: Interrupt notification of Memory 5 non-correctable error events is disabled

ESCIE6 00: Interrupt notification of Memory 6 single-bit correction events is disabled

ENCIE6 00: Interrupt notification of Memory 6 non-correctable error events is disabled

ESCIE7 00: Interrupt notification of Memory 7 single-bit correction events is disabled

ENCIE7 00: Interrupt notification of Memory 7 non-correctable error events is disabled

CR1 00000000 ESCIE8 00: Interrupt notification of Memory 8 single-bit correction events is disabled

ENCIE8 00: Interrupt notification of Memory 8 non-correctable error events is disabled

ESCIE9 00: Interrupt notification of Memory 9 single-bit correction events is disabled

ENCIE9 00: Interrupt notification of Memory 9 non-correctable error events is disabled

ESCIE10 00: Interrupt notification of Memory 10 single-bit correction events is disabled

ENCIE10 00: Interrupt notification of Memory 10 non-correctable error events is disabled

ESCIE11 00: Interrupt notification of Memory 11 single-bit correction events is disabled

ENCIE11 00: Interrupt notification of Memory 11 non-correctable error events is disabled

ESCIE12 00: Interrupt notification of Memory 12 single-bit correction events is disabled

ENCIE12 00: Interrupt notification of Memory 12 non-correctable error events is disabled

ESCIE13 00: Interrupt notification of Memory 13 single-bit correction events is disabled

ENCIE13 00: Interrupt notification of Memory 13 non-correctable error events is disabled

ESCIE14 00: Interrupt notification of Memory 14 single-bit correction events is disabled

ENCIE14 00: Interrupt notification of Memory 14 non-correctable error events is disabled

ESCIE15 00: Interrupt notification of Memory 15 single-bit correction events is disabled

ENCIE15 00: Interrupt notification of Memory 15 non-correctable error events is disabled

CR2 00000000 ESCIE16 00: Interrupt notification of Memory 16 single-bit correction events is disabled

ENCIE16 00: Interrupt notification of Memory 16 non-correctable error events is disabled

ESCIE17 00: Interrupt notification of Memory 17 single-bit correction events is disabled

ENCIE17 00: Interrupt notification of Memory 17 non-correctable error events is disabled

ESCIE18 00: Interrupt notification of Memory 18 single-bit correction events is disabled

ENCIE18 00: Interrupt notification of Memory 18 non-correctable error events is disabled

ESCIE19 00: Interrupt notification of Memory 19 single-bit correction events is disabled

ENCIE19 00: Interrupt notification of Memory 19 non-correctable error events is disabled

SR0 00000000 SBC0 00: No single-bit correction event on Memory 0 detected

NCE0 00: No non-correctable error event on Memory 0 detected

SBC1 00: No single-bit correction event on Memory 1 detected

NCE1 00: No non-correctable error event on Memory 1 detected

SBC2 00: No single-bit correction event on Memory 2 detected

NCE2 00: No non-correctable error event on Memory 2 detected

SBC3 00: No single-bit correction event on Memory 3 detected

NCE3 00: No non-correctable error event on Memory 3 detected

SBC4 00: No single-bit correction event on Memory 4 detected

NCE4 00: No non-correctable error event on Memory 4 detected

SBC5 00: No single-bit correction event on Memory 5 detected

NCE5 00: No non-correctable error event on Memory 5 detected

SBC6 00: No single-bit correction event on Memory 6 detected

NCE6 00: No non-correctable error event on Memory 6 detected

SBC7 00: No single-bit correction event on Memory 7 detected

NCE7 00: No non-correctable error event on Memory 7 detected

SR1 00000080 SBC8 00: No single-bit correction event on Memory 8 detected

NCE8 00: No non-correctable error event on Memory 8 detected

SBC9 00: No single-bit correction event on Memory 9 detected

NCE9 00: No non-correctable error event on Memory 9 detected

SBC10 00: No single-bit correction event on Memory 10 detected

NCE10 00: No non-correctable error event on Memory 10 detected

SBC11 00: No single-bit correction event on Memory 11 detected

NCE11 00: No non-correctable error event on Memory 11 detected

SBC12 00: No single-bit correction event on Memory 12 detected

NCE12 00: No non-correctable error event on Memory 12 detected

SBC13 00: No single-bit correction event on Memory 13 detected

NCE13 00: No non-correctable error event on Memory 13 detected

SBC14 01: Single-bit correction event on Memory 14 detected

NCE14 00: No non-correctable error event on Memory 14 detected

SBC15 00: No single-bit correction event on Memory 15 detected

NCE15 00: No non-correctable error event on Memory 15 detected

SR2 00000000 SBC16 00: No single-bit correction event on Memory 16 detected

NCE16 00: No non-correctable error event on Memory 16 detected

SBC17 00: No single-bit correction event on Memory 17 detected

NCE17 00: No non-correctable error event on Memory 17 detected

SBC18 00: No single-bit correction event on Memory 18 detected

NCE18 00: No non-correctable error event on Memory 18 detected

SBC19 00: No single-bit correction event on Memory 19 detected

NCE19 00: No non-correctable error event on Memory 19 detected

EAR0 00000000 EAR 00000000

SYN0 00000000 SYNDROME 00

EAR1 00000000 EAR 00000000

SYN1 00000000 SYNDROME 00

EAR2 00000000 EAR 00000000

SYN2 00000000 SYNDROME 00

EAR3 00000000 EAR 00000000

SYN3 00000000 SYNDROME 00

EAR4 00000000 EAR 00000000

SYN4 00000000 SYNDROME 00

EAR5 00000000 EAR 00000000

SYN5 00000000 SYNDROME 00

EAR6 00000000 EAR 00000000

SYN6 00000000 SYNDROME 00

EAR7 00000000 EAR 00000000

SYN7 00000000 SYNDROME 00

EAR8 00000000 EAR 00000000

SYN8 00000000 SYNDROME 00

EAR9 00000000 EAR 00000000

SYN9 00000000 SYNDROME 00

EAR10 00000000 EAR 00000000

SYN10 00000000 SYNDROME 00

EAR11 00000000 EAR 00000000

SYN11 00000000 SYNDROME 00

EAR12 00000000 EAR 00000000

SYN12 00000000 SYNDROME 00

EAR13 00000000 EAR 00000000

SYN13 00000000 SYNDROME 00

EAR14 40040790 EAR 40040790

SYN14 46000000 SYNDROME 46

EAR15 00000000 EAR 00000000

SYN15 00000000 SYNDROME 00

EAR16 00000000 EAR 00000000

SYN16 00000000 SYNDROME 00

EAR17 00000000 EAR 00000000

SYN17 00000000 SYNDROME 00

EAR18 00000000 EAR 00000000

SYN18 00000000 SYNDROME 00

EAR19 00000000 EAR 00000000

SYN19 00000000 SYNDROME 00

davidtosenovjan PetrS Please help

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have just downloaded and tested Davids code and it is reporting in ERM after 1-bit error is injected as expected.

See my screenshot bellow:

I did no modification to it, just run it.

regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

Thanks for you speedy reply. Even i am able to get SBC14 01: Single-bit correction event on Memory 14 detected as shown in the log file above but in my case IVOR1 exception is not being raised and machine_Check_Handler is not being called. i have even attatched my core registers log for your reference. my

MSR 02008000 .

Please help how can i get my IVOR1 handler to work i am using the same startup files as given in the example project.

Thank you,

Regards

Michael Jihan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

That's correct.

Single bit will not cause exception. As the single bit event is automatically repaired by ECC machine.

However multibit ECC will cause IVOR1.

For multibit you have to enable it in example code.

regards,

Peter