- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- ADC Self Test for MPC5xxx family.

ADC Self Test for MPC5xxx family.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC Self Test for MPC5xxx family.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to do ADC-self test for MPC5xxx family. When I enable ADC_0_STAW0R[WDTE] algorithm S timeout value. I am always seeing ADC_0_STSR1[WDTERR]. I have my ADC_0_STBRR[WDT] as 50ms.

1. Why is the ADC_0_STSR1[WDTERR] bit is set? Is there a sequence to enable ADC_0_STAW0R[WDTE]?

In the spec for ADC_0_STAW0R[WDTE] the description is as below.

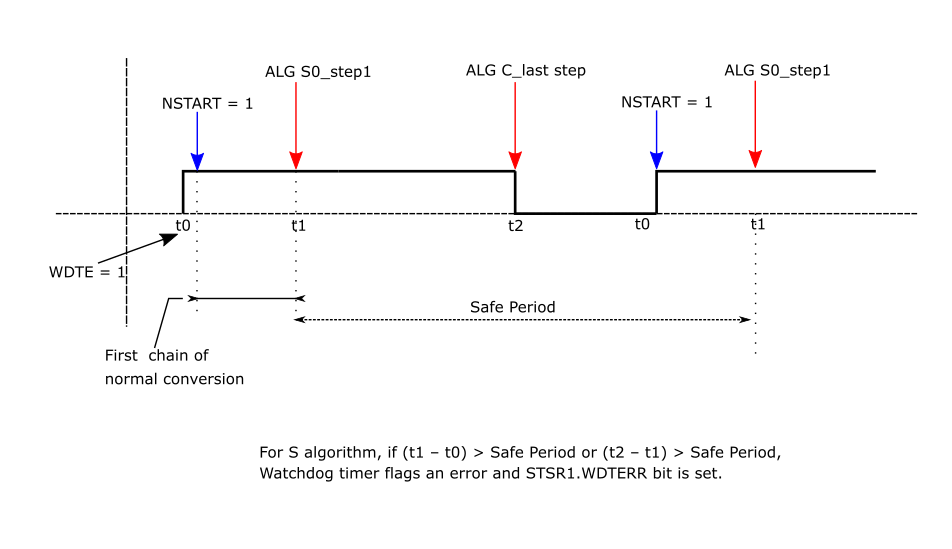

Watchdog timer enable (related to the algorithm S).

Enables/disables the watchdog timer monitoring function for all ADC Supply self test steps.

The watchdog timer verifies:

• Correct sequence of the algorithm (step sequence)

• Execution of the algorithm within the safe time period as defined by STBRR[WDT]

As soon as the watchdog timer is enabled, execution must be detected within the safe time period. The

watchdog timer is reset each time the algorithm restarts.

This bit should be set only in scan mode.

0 Disabled

1 Enabled

2. what does it mean execution must be detected within safe time period?

Any help would be much appreciated.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

1. Why is the ADC_0_STSR1[WDTERR] bit is set? Is there a sequence to enable ADC_0_STAW0R[WDTE]?

I expect you are not performing these tests periodically. This Watchdog is watching time between 2 ADC selts tests in application. For example FTTI is 1s. This means after ADC self test is executed next one must take place within 1sec.

So it is watchdog between tests, not test watchdog.

Please read carefully watchdog chapter in reference manual.

regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.. I corrected the sequence to enable WDTE, it is working as expected.