- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5777M EBI for exteranl flash and SRAM

MPC5777M EBI for exteranl flash and SRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5777M EBI for exteranl flash and SRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We use a external flash and a external SRAM on our own board.

We use the 16-bit bus mode and DATA[16:31] signals.

CS0: 0x20000000 --- 0x20FFFFFF

CS1: 0x21000000 ---- 0x203FFFFF

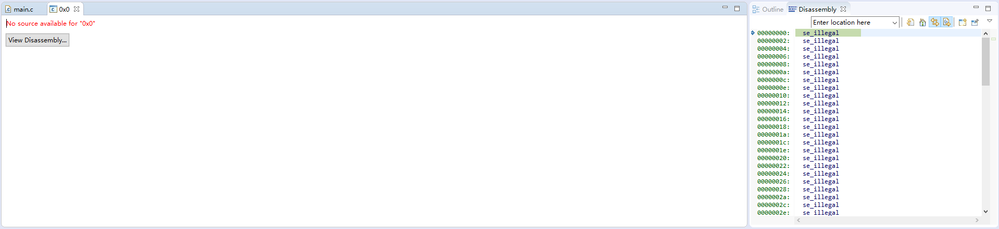

I make test code as the attachment file, it can't write data to external SRAM and the CS1 have no action.

I don't know if the configuration is right.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I count point out following example code where you can see how to configure external SRAM. Unfortunatelly it is written for different device, so you will have to port it to MPC5777M. As MPC5777MEVB does not have external SRAM installed on the board, I don't see a need of such example. I believe MPC5777C example could be useful as EBI module is almost the same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you, I just transplant the mpc5777C examlpe to my attachment, It can't work. So I ask this question. Could you help check my configuration? And I found some code in MPC5777C example:

static asm void External_SRAM_MMU_init(void)

{

//nofralloc

e_lis r3, 0x1002 /* Select TLB entry #, define R/W replacment control */

mtMAS0 r3 /* Load MAS0 with 0x1002 0000 for TLB entry #2 */tlbre /* Get TLB entry # information */

mfspr r3, MAS3

//oris r3, r3, 0x2000 /* EBI Physical Base Addr changed to 0x2000_0000 */

//ori r3, r3, 0x0000

se_bseti r3,2

e_ori r3,r3,0x0000

mtMAS3 r3

msync /* make sure we finished all memory accesses */

tlbwe /* Write entry defined in MAS0 (entry 1 here) to MMU TLB */

se_isync /* Wait for tlbwe to complete, then flush instruction buffer */

//blr

}

For MPC5777M, how to configure MMU?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There is MMU on the MPC5777M. This does not need to be done.