- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- 4bit transfer on LPSPI

4bit transfer on LPSPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

4bit transfer on LPSPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Further my test to get the maximum throughput form the LPSPI port, I tried to enable the 4bit mode for TX only.

A part from the standard LPSPI test, which I posted in another thread with a nearly working result, I added the following code to enable the 4bit TX transfer.

// enable the 4bit transfer

LPSPI3->TCR &= ~(LPSPI_TCR_TXMSK_MASK); // enable TX

LPSPI3->TCR |= LPSPI_TCR_RXMSK_MASK; // disable RX

LPSPI3->TCR &= ~(LPSPI_TCR_WIDTH_MASK);

LPSPI3->TCR |= LPSPI_TCR_WIDTH(2); // 4bit transfer

// set the pin

LPSPI3->CFGR1 |= LPSPI_CFGR1_PCSCFG(1);

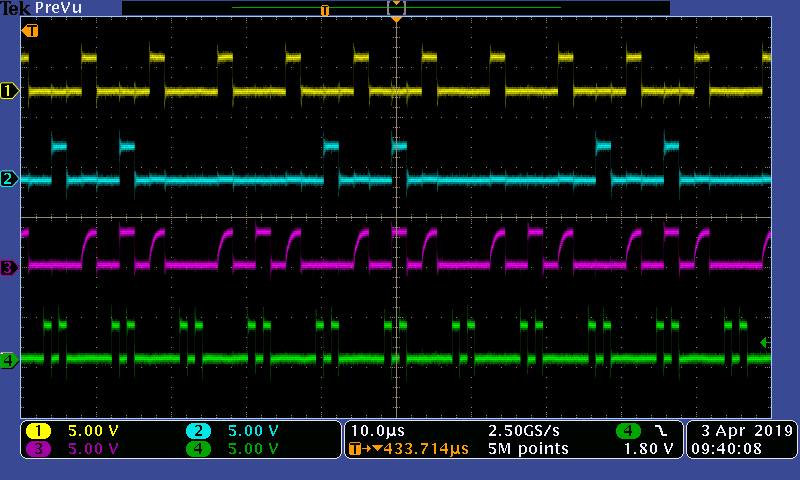

Hey, I can see the data of 4bit on the bus, but there are something does not look very right,

1) in 4bit mode, the clock should only issue 2 pulses, but from the waveform there are 4;

2) the gap (165ns) between each transfer becomes unbearable. PS, should the TX FIFO take care of those gaps?

any idea? thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content