- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- SPI configuration master/slave S32K148

SPI configuration master/slave S32K148

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to configure LPSPI on S32K148 both for master and slave mode. For master I use LPSPI0, slave will be LPSPI1.

This is my master configuration:

void SPI_master_init()

{

// LLSPI0

PCC->PCCn[PCC_LPSPI0_INDEX] = 0;

// SPLLDIV2

PCC->PCCn[PCC_LPSPI0_INDEX] = PCC_PCCn_PR(1) | PCC_PCCn_CGC(1) | PCC_PCCn_PCS(0b110);

LPSPI0->CR = 0;

LPSPI0->IER = 0;

LPSPI0->DER = 0;

LPSPI0->CFGR0 = 0;

LPSPI0->CFGR1 = LPSPI_CFGR1_MASTER(1);

LPSPI0->TCR = LPSPI_TCR_CPHA_MASK | LPSPI_TCR_PRESCALE(2) | LPSPI_TCR_PCS(3) | LPSPI_TCR_FRAMESZ(15);

LPSPI0->CCR = LPSPI_CCR_SCKPCS(4) | LPSPI_CCR_PCSSCK (9) | LPSPI_CCR_DBT(8) | LPSPI_CCR_SCKDIV(8);

LPSPI0->FCR = LPSPI_FCR_TXWATER(3) | LPSPI_FCR_RXWATER(0);

LPSPI0->CR = LPSPI_CR_DBGEN(1) | LPSPI_CR_MEN(1);

}

This is my slave configuration

void SPI_slave_init()

{

// LLSPI1

PCC->PCCn[PCC_LPSPI1_INDEX] = 0;

// SPLLDIV2

PCC->PCCn[PCC_LPSPI1_INDEX] = PCC_PCCn_PR(1) | PCC_PCCn_CGC(1) | PCC_PCCn_PCS(0b110);

LPSPI1->CR = 0;

LPSPI1->IER = 0;

LPSPI1->DER = 0;

LPSPI1->CFGR0 = 0;

LPSPI1->CFGR1 = LPSPI_CFGR1_MASTER(0) | LPSPI_CFGR1_AUTOPCS(1);

LPSPI1->TCR = LPSPI_TCR_CPHA(1) | LPSPI_TCR_PRESCALE(2) | LPSPI_TCR_PCS(3) | LPSPI_TCR_FRAMESZ(15);

LPSPI1->FCR = LPSPI_FCR_TXWATER(3) | LPSPI_FCR_RXWATER(0);

LPSPI1->CR = LPSPI_CR_DBGEN(1) | LPSPI_CR_MEN(1);

}

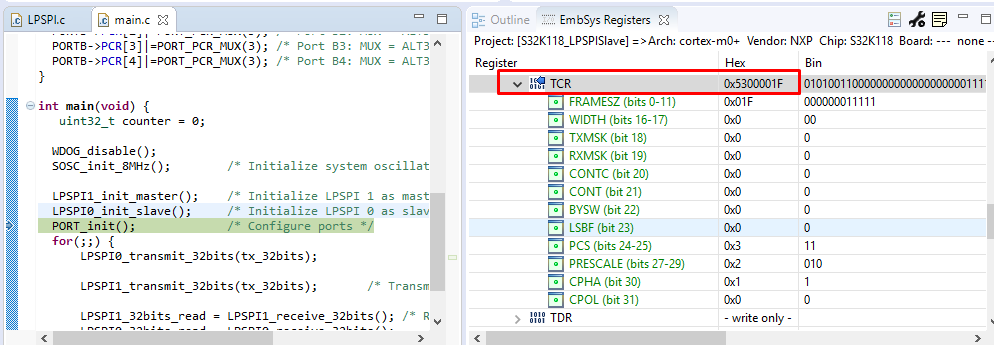

During debugging, I cannot see that register TCR is changing, but I can see, that data words are being transmitted to FIFOs. To be more precise on 'TCR is not changing', I had a look in the resigters view of S32 Design Studio and never saw any other value but the reset value for that register. Things are the same both for master and slave configuration.

My question is: How can I check, that TCR is set correctly?

As you can see from my code, I do not use the S32 SDK by purpose.

Any help resolving that issue would be appriciated.

Kind Regards,

Michael

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Michael,

The LPSPI master example for the S32K144 is available in the S32DS -> file -> new-> S32DS Projet from Example.

So, I have tried to add the LPSPI slave into this example. And it's working for me. (see attachment)

The LPSPI1 is configured as Master and LPSPI0 is configured as Slave.

Master and Slave transmit 0xFD00 value and also both receive this value.

Is needed to connect pins:

PTD0 with PTB2

PTD1 with PTB4

PTD2 with PTB1

I have not a problem with reading of this register. However, I would like to recommend you do not read this register. I'm not sure why you need to read the TCR register.

I hope it helps.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

hello Razvan,

I did have a look at the cookbook, which and tried to adapt it to the situation Diana described. However, I could not send any data and started to track down the issue. What I directly saw was that TCR is not being updated, so this is why I started this thread.

I will try to get Diana's example running, but it looks pretty much the same, I already tried.

Best Regads,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Michael,

I have more projects for different MCU so, I made a mistake in the connection description.

Please, see the connection update:

PTD0 with PTB2

PTD1 with PTB1

PTD2 with PTB3

How does it work?

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

I tried running the code in s32k148 but the data is not received in the receive data variable as Rx buffer always reads 0. I have a query can we configure one peripheral as master and one as slave in the same device as the transmit and receive data register addresses remain same for all LPSPIs.

Please help me with this issue.

Thanks in advance.

Regards,

Saikumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

I was busy in office, thus sorry for replying only now.

Your example project works for me, thank you very much!

As it turned out, I had a clocking issue. The following lines were missing in my initialization of SPLL:

SCG->SPLLCSR = SCG_SPLLCSR_SPLLEN(0);

SCG->SPLLDIV = SCG_SPLLDIV_SPLLDIV1(2) | SCG_SPLLDIV_SPLLDIV2(4); /* SPLLDIV1 divide by 2; SPLLDIV2 divide by 4 */

Best Regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

thank you for your reply. I only returned to office today, so I could not do any further tests yet.

You mentioned in your post, that the register view in S32DS should reflect the correct state of the TCR register. As I did write in my post, that I already had a look in that view, I wonder how it is possible, that the register value is always displayed as 0x1F (the reset value) after initialization? I already tried to read TCR multiple times as suggested in RM, but that did not change anything..

Could you provide some demo code, which initializes SPI master and slave without usage of the SDK?

Thank you and

Best Regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Michael,

The LPSPI master example for the S32K144 is available in the S32DS -> file -> new-> S32DS Projet from Example.

So, I have tried to add the LPSPI slave into this example. And it's working for me. (see attachment)

The LPSPI1 is configured as Master and LPSPI0 is configured as Slave.

Master and Slave transmit 0xFD00 value and also both receive this value.

Is needed to connect pins:

PTD0 with PTB2

PTD1 with PTB4

PTD2 with PTB1

I have not a problem with reading of this register. However, I would like to recommend you do not read this register. I'm not sure why you need to read the TCR register.

I hope it helps.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can take a look over this cookbook. It is designed to S32K144, but you can easily port it to S32K148.

https://www.nxp.com/docs/en/application-note/AN5413.pdf

Best regards,

Razvan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Michael,

I would like to mention a few details from the RM rev. 9.:

1.

"Avoid register reading problems: Reading the Transmit Command Register will return

the current state of the command register. Reading the Transmit Command Register at the

same time that the Transmit Command Register is loaded from the transmit FIFO, can

return an incorrect Transmit Command Register value. It is recommended:

• to either read the Transmit Command Register when the transmit FIFO is empty,

• or to read the Transmit Command Register more than once and then compare the

returned values."

2.

"49.4.3 Slave Mode

LPSPI slave mode:

• uses the same shift register and logic that master mode uses

• does not use the Clock Configuration Register (CCR)

• during SPI bus transfers, requires that the Transmit Command Register (TCR)

remain static (unchanging)"

After initialization, you can look at the register setting in the S32DS and see that the TCR register is set.

For example:

I hope it helps.

Best Regards,

Diana