- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Digital Signal Controllers

- :

- PTN3460I

PTN3460I

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PTN3460I

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am writing to because I want to use the chip PTN3460I to bridge between DP and LVDS. I want to use the chip without any external EEPROM. I want save all the setting in the internal EEPROM. because we don't have planned to develop specific software to configure the chip and, in the case, to reconfigure it any time that we launch our application.

I have tried to use the DPCD_M program to try to configure the chip "off-line". The program recognize the chip, it seems that is able to read internal EEPROM, but if I try to write the internal EEPROM, it is not able to change the values. So not I am stopped and I need any suggestion about that. Please, could somebody be so kind to help me? Thank you in advance. Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

PTN3460I offers two ways to initialize the configuration table:

- Read it from internal flash memory.

- Read it from an external EEPROM.

PTN3460I firmware will first check DEV_CFG pin (pin 12 of PTN3460I) status during initialization stage, and it will read 1K bytes configuration table from external EEPROM if DEV_CFG pin is high, otherwise it will read 1K bytes configuration table from internal flash memory.

PTN3460I firmware uses all zero to initialize configuration table in SRAM in following two cases

- If DEV_CFG pin = high, but no external EEPROM exists.

- If DEV_CFG pin = open or low, but the magic number in the configuration table in internal flash is incorrect.

EDID ROM emulation bit is programmed in the configuration table inside the flash memory. It can also be configured through pin setting. FW will read in the pin settings and overwrite the configuration table settings. CFG4 pin is used to turn EDID emulation bit ON/OFF (see Table 14 of the PTN3460I datasheet for more details).

There is an application note that provides detailed explanations for the configuration table, programming method, and how to program EDID and configuration setting into PTN3460I internal flash.

Please find the Application note AN11606 “PTN3460I Programming guide” in the following link: AN11606: https://www.nxp.com/docs/en/application-note/AN11606.pdf

In case you need further assistance, I would need to know more details regarding the customer and application, please answer to the following questions in case you need further support:

- Website of the customer company.

- Company location.

- End product(s) and application.

4. Targeted production date or timeframe.

5. Projected volume/quantity.

Have a great day,

Jose

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kind Jose,

thank you very much for your answer.

I have made all the suggested checks on the schematics, but it seems that everything is ok and the system doesn't work.

In my opinion it is strange that the chip presents to the GPU with 800 x 480 @60Hz resolution (it seems that it is using EDID 1) but we have not made any change.

I have no further ideas how to set it in the correct way. Please could you be so kind to tell me which is the correct way to configure the chip in the way to use EDID0 (1024 x 768 @60Hz resolution) using your DPCD M Tool (so configure the chip through DP AUX channel), because we have no possibility to configure it via I2C? I have tried, but I was no able to write any memory cell.Moreover, pleae could you be so kind to write me the meaning of the address that I inset in the DPCD M Tool: is it the address in the SRAM or the equivalent used in the I2C communication?

In our configuration:DEV_CFG is low;

CFG1 is low;

CFG2 is low;

CFG3 is high.

Thank you very much for your assistence. If you need any further information, please ask me.

Waiting for you kind answer.

Best regards.

Francesco Palma

f.palma@yahoo.it

Il venerdì 29 marzo 2019, 16:38:39 CET, reyes <admin@community.nxp.com> ha scritto:

|

NXP Community |

|

Re: PTN3460I

reply from Jose Alberto Reyes Morales in Digital Signal Controllers - View the full discussion

Hi,

PTN3460I offers two ways to initialize the configuration table:

- Read it from internal flash memory.

- Read it from an external EEPROM.

PTN3460I firmware will first check DEV_CFG pin (pin 12 of PTN3460I) status during initialization stage, and it will read 1K bytes configuration table from external EEPROM if DEV_CFG pin is high, otherwise it will read 1K bytes configuration table from internal flash memory.

PTN3460I firmware uses all zero to initialize configuration table in SRAM in following two cases

- If DEV_CFG pin = high, but no external EEPROM exists.

- If DEV_CFG pin = open or low, but the magic number in the configuration table in internal flash is incorrect.

EDID ROM emulation bit is programmed in the configuration table inside the flash memory. It can also be configured through pin setting. FW will read in the pin settings and overwrite the configuration table settings. CFG4 pin is used to turn EDID emulation bit ON/OFF (see Table 14 of the PTN3460I datasheet for more details).

There is an application note that provides detailed explanations for the configuration table, programming method, and how to program EDID and configuration setting into PTN3460I internal flash.

Please find the Application note AN11606 “PTN3460I Programming guide” in the following link: AN11606: https://www.nxp.com/docs/en/application-note/AN11606.pdf

In case you need further assistance, I would need to know more details regarding the customer and application, please answer to the following questions in case you need further support:

- Website of the customer company.

- Company location.

- End product(s) and application.

4. Targeted production date or timeframe.

5. Projected volume/quantity.

Have a great day,

Jose

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fracesco,

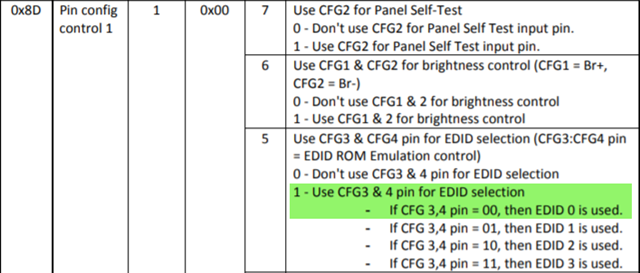

There is a way to select EDID 0 by setting bit 5 of register 0x8D (Pin config control 1) and connecting CFG3 and CFG4 pins to LOW…

*Image from page 20 of the application note AN11606: https://www.nxp.com/docs/en/application-note/AN11606.pdf

But, I'm not sure if this works fine for you since you mentioned that “we don't have planned to develop specific software to configure the chip”

I hope this helps.

Thanks,

Jose