- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- spdif record_playback latency is unstable

spdif record_playback latency is unstable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

spdif record_playback latency is unstable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

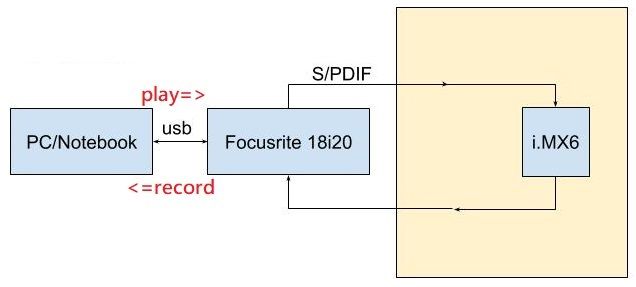

We use i.MX6 for audio processing, do ASRC to fixed S/PDIF input in 48kHz.

Without any process, i.MX6 direct pass 48kHz S/PDIF to output.

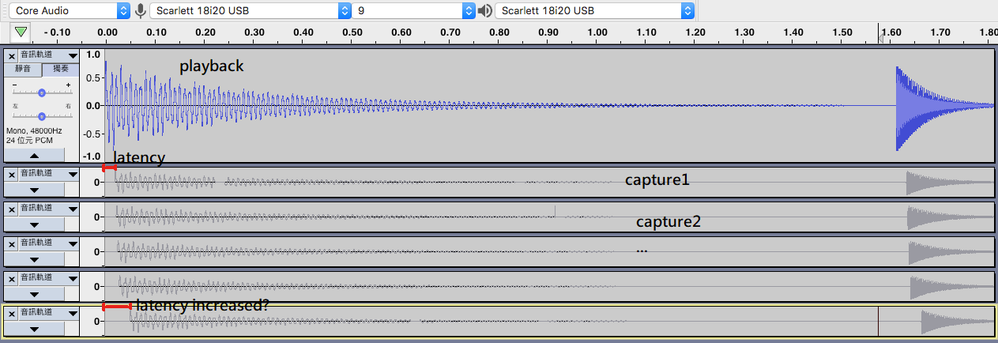

The latency between playback(to i.MX6) and recording(from i.MX6) will increase.

Environment

- PC software

- [Audacity]

- play and record

- i.MX6

- $ alsaloop -P sysdefault:CARD=imxspdif -C sysdefault:CARD=imxspdif -r 48000 -t 8192 -vvvv -f S16_LE

- the argument [-t] won't change result

- Latency between PC and Focusrite is 5ms and it is very stable

- PC => Focusrite spdif out => Focusrite spdif in => PC

Logs and observation

- alsaloop log, please refer to the attachment

- expected clock rate = 227328000

- actual clock rate = 227368421

- set sample rate to 48008Hz for 48000Hz playback

- many underruns for playback

- many times do resync

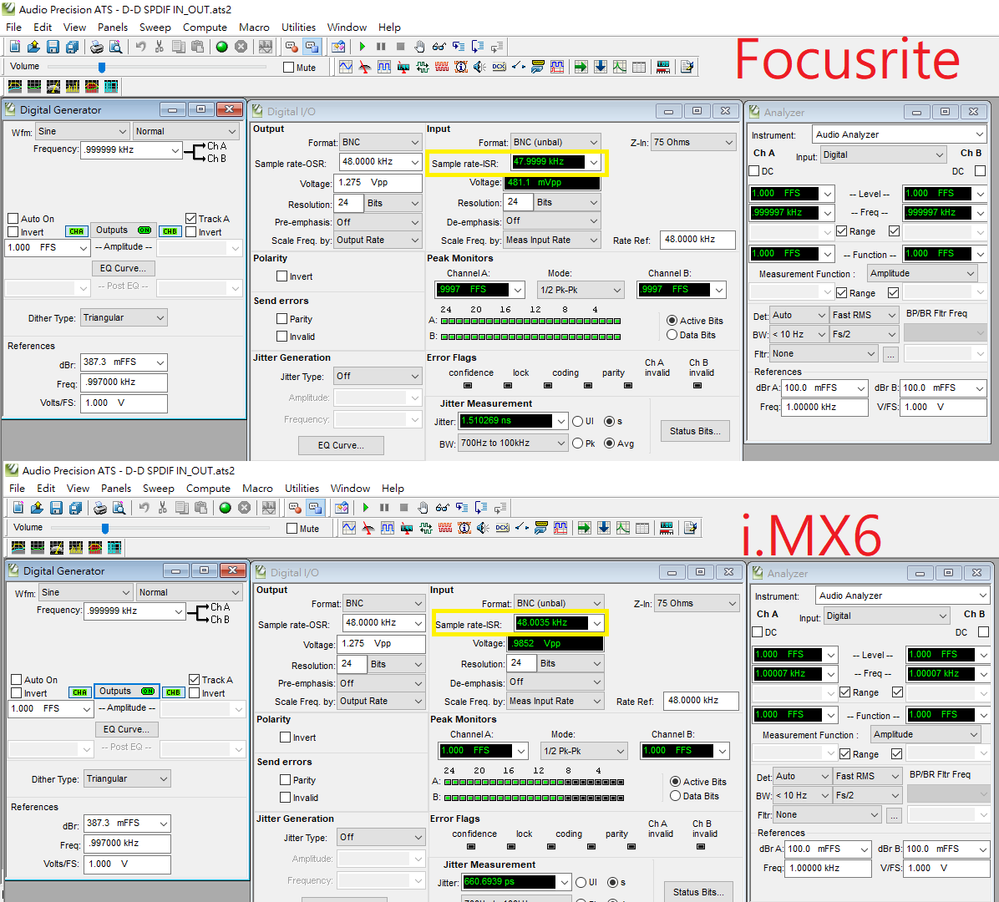

- Audio Precision, measure spdif out for Focusrite and i.MX6

- Focusrite sample rate 47999.9 Hz (diff < 0.1)

- i.MX6 sample rate 48003.5 Hz (diff > 3.5)

- Latency increase until XRUN occur

Source code and Setting

- Linux imx6qsabresd 4.9.88-PgFx+

- imx6qdl.dtsi:

Question

- Why does the latency increase ( until underrun occurs ) ?

- Why actual CPU clock differ than expected clock ?

- How to bypass i.MX6, directly pass spdif-IN to spdif-OUT ?

Thanks,

William

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi William

nxp linux does not provide any specific or guaranteed latencies, so

one can try to analyze latencies using description of spdif driver in

sect.7.4 The Sony/Philips Digital Interface (S/PDIF) attached Linux Manual

and AN4553 Using Open Source Debugging Tools for Linux on i.MX Processors

https://www.nxp.com/docs/en/application-note/AN4553.pdf

Also may be recommended to try extended support with Professional Services

NXP Professional Services | NXP

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igor,

Thank you for your prompt reply.

About the latency, my concern is not "how low" but "how stable".

We believe that something may happen causing an increase in latency, e.g., choose a wrong clock source.

First we have a stable experimental environment, then we discuss and debug how to reduce latency.

We know i.MX processor will do ASRC or something processing between receive spdif and transmit spdif, so we would like to know how to bypass all processing, e.g., modify SPDIF_SCR, SPDIF_SRPC, etc.

Thanks,

William