- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Enabling Mass storage Host and HID device in LPC4357 and Mass storage stuck in HOST_STATE_Powered_WaitForDeviceSettle state

Enabling Mass storage Host and HID device in LPC4357 and Mass storage stuck in HOST_STATE_Powered_WaitForDeviceSettle state

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Enabling Mass storage Host and HID device in LPC4357 and Mass storage stuck in HOST_STATE_Powered_WaitForDeviceSettle state

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we mentioned earlier we are using LCP4357 - using USB1 as Mass storage host and USB0 as HID device. For HD device we are using ROM USB Stack and using NXPUSBLib for mass storage host. When we enable each separately things work – that means we are able to write a small file into a USB stick and we have established a minimum HID communication with a HID host. However, when we enable HID device and connect USB stick, the USB Host state machine stays in the HOST_STATE_Powered_WaitForDeviceSettle state (the program gets stuck in FSUSB_DiskInsertWait -- because USB1_IRQHandler keeps getting invoked and puts the state in Powered State). However, when the HID device is not enabled, and the USB stick is connected, the interrupt occurs (USB1_IRQHandler) only once and able to write to the device because the state machine puts the state in Host Configured State.

Any idea why the interrupt keeps occurring?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we mentioned earlier, both Stack are using USB RAM address 0x2000 0000. In the USB host driver USBRAM_SECTION is at

0x2000 0000.

For the Rom driver, USB_STACK_MEM_BASE is at 0x2000 0000. For USB0 ENDPOINTLISTADDR is set at 0x2000 0000. I guess we shouldn’t change that?

How to resolve this? Which one should we change?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi S S,

Thanks for your sharing.

I agree with you that RAM overlap may be the cause.

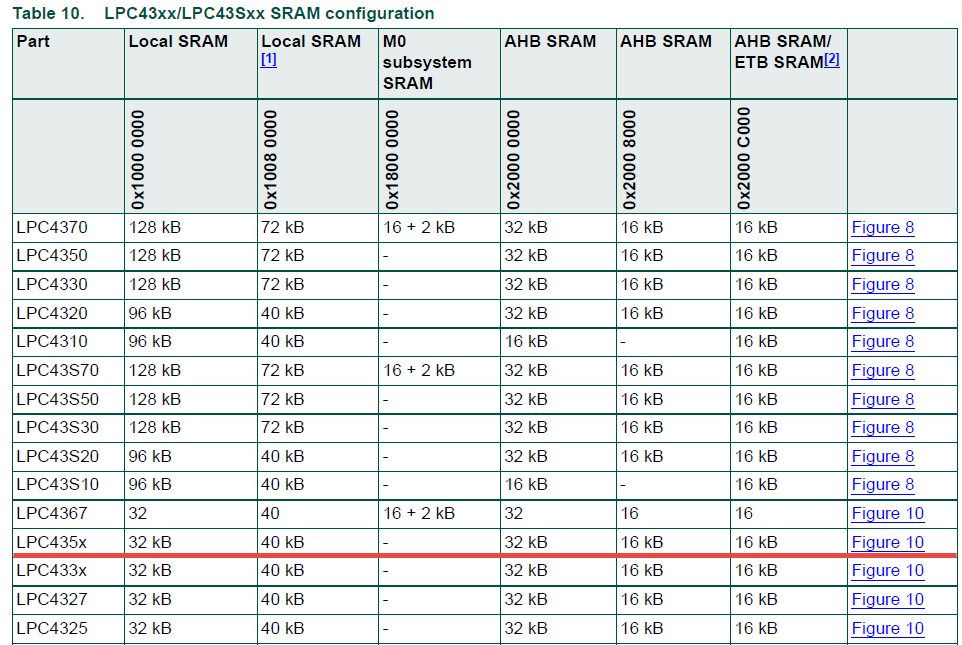

Fig 1

The LPC4357 has several parts of RAMs, I'd like to suggest that you can assign two parts of RAM to the USB1 and USB0 respectively.

For instance, the 0x2000_0000~0x2000_2000 is assigned for ROM USB stack.

/* On LPC18xx/43xx the USB controller requires endpoint queue heads to start on

a 4KB aligned memory. Hence the mem_base value passed to USB stack init should

be 4KB aligned. The following manifest constants are used to define this memory.

*/

#define USB_STACK_MEM_BASE 0x20000000

#define USB_STACK_MEM_SIZE 0x00002000

Meanwhile, USB1 stack is located in AHB SRAM section (0x20008000~0x200C0000), thus they're independent with each other.

Please give a try.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

However Host Mass storage needs around 0x5088 bytes (according to our map

file) and at the address you mentioned there are only 0x4000 bytes. Anyway

I did try to build and linker fails as expected and gives the following

message.

unable to allocate space for sections/blocks with a total

estimated minimum size of 0x4688 bytes (max align 0x1000) in

<[0x2000'8000-0x2000'bfff]> (total uncommitted space 0x4000).

Can we allocate that space to USB1 (ROM Stack) How much space does ROM

stack need?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

It's okay to allocate the 0x20000000~0x20008000 to the USB1 and 0x20008000~0x2000C000 to the USB0, as the ROM stack would need 0x2000 bytes space.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Further debugging indicates that two stacks are using USB RAM and that causes the problem.

(we are not 100% sure why the interrupt keeps occurring, but first enumeration process fails due to insufficient memory) In the NXPUSBlib - Pipe_ConfigurePipe function USB_Memory_Alloc is not able to allocate the buffer for Pipe_info.buffer, so the enumeration process fails. Now the question is when we are invoking two stacks, how do we allocate separate USB memory space. Is it as simple as setting two separate base address for two different stacks?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have sent the files through an email .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, TIC. Happy to do it. We are using IAR workbench. Should I send *.hex, *.sim and *.out files? Also, also how to get a USB trace file?

In our board, we have no external PHY for USB1. So USB1 - Mass storage host in our product and USB0 - HID device.

USB0 - HID device.

After enabling both USB ROM stack(USB0) and HOST stack for USB1, we are calling a function that writes a small file into USB. When we switch on the system by inserting a USB stick, we encounter the problem we described earlier. The program execution never comes out of the write a file to USB function because of the problem we described earlier. Everything else is the same, but when we run the program without inserting a USB stick, things work as expected because the USB write function which internally calls f_open, detects that there is no stick and without the USB device there won't be any device connect interrupt.

Since I am not able to upload files here, I am sending those files through an email.

I am sending the files as it is. If you run into problems due to our custom board, please let me know.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Further explanation on this problem

Without enabling USB0 ROM Stack, when we connect a mass storage device to our product, as expected only once port Status – Connect Status interrupt occurs – 0x4000 – 7184 register bit 1 (Connected Status bit) is high. However, when we enable USB0 ROM Stack, USB1 port Status – Connect Status interrupt keeps occurring. In this case when the interrupt occurs for the first time,

register 0x4000 7140 value will be 0x00008025 and

register 0x4000 7144 – 0x00008088 (these values are the same as when the Rom Stack is not enabled and the connect Status interrupt occurs)

However, when the connect interrupt status interrupt keeps occurring –

register 0x4000 7140 value will be 0x00080b00.

Register 0x4000 7144 will be 0x00001080

Any idea?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

I think I need to learn more information about the issue, thus I was wondering if you can share a compile-able demo which can replicate the issue, in additional, introduce the testing process in details, I will run the demo with the MCB4357 board.

And that would be better if you can upload the USB trace file.

Looking forward to your reply.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

I'm working on it now.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------