- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1012A SDHC1 EMMC problem

LS1012A SDHC1 EMMC problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LS1012A SDHC1 EMMC problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP Team,

We are designing LS1012A(LS1012AXN7HKA) based custom board and we configure both SDHC interface.

SDHC1 is using for emmc support and SDHC2 is using for emmc too.

Emmc on the second eSDHC controller work normally.But Emmc on the first eSDHC controller does not work normally.

- SDHC1_CMD, SDHC1_CLK, SDHC1_DATA[3:0] are connected to the corresponding pins of eMMC;

- SDHC1_CD_B is pulled up to O2VDD with a 10K resistor; SDHC1_WP is pulled down to GND through 1K resistance. SDHC1_VSEL is suspended (the development board is connected to the power chip MC34VR5100A1EP to control the voltage switch of SDHC1 interface power supply VCC_EVDD);

- SDHC1 interface power supply VCC_EVDD is always 1.8v.

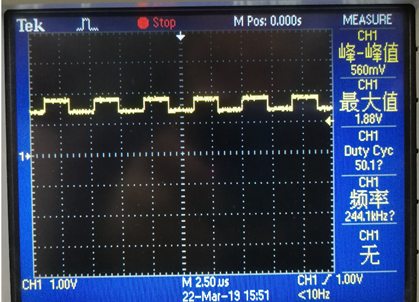

It could not read and write to the eMMC after cold start, Through measuring the SDHC1 interface related pins in LS1012A with an oscilloscope, it was found that the waveform of the pin of eMMC was abnormal during the abnormal operation, and it could not drive to the low level state. The waveform of SDHC1_CLK pin is intercepted as follows:

But after power on for about 2.5 minutes, the eMMC worked normally. The emmc on the first eSDHC controller can read and write normally

Any pointers are greatly appreciated.

Have a great day,

Diao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Set below configurations in RCW can solve the problem.

SDHC1_VSEL=0

EVDD_VSEL=1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diao! Did the last suggestion to set SDHC1_VSEL and EVDD_VSEL to 0b00 help your problem? I am also interested in using SDHC1 for eMMC and I would really appreciate to if you'll share whether you've got it working in the end.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, ufedor

1. 62 pin (QSPI_A_SCK) is directly connected to QSPI NORFLASH without pull up and down.

2. 127 pin(SDHC2_CLK) is connected with eMMC mtfc64gakaeyf-4mit clock pin, which is pulled up to O1VDD through a 10K resistor;

3. 71 pin (SDHC1_CLK) is connected to eMMC mtfc64gakaeyf-4mit clock pin, and is pulled up to EVDD through a 10K resistor (in this design, EVDD = 1.8v, O1VDD, O2VDD and EVDD use the same power network)

4. 66 pin(SCAN_MODE_B) is pulled up to O1VDD through a 1K resistor.

I will be glad to any advice. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) use a scope to ensure that the signal is not low during POR.

5) confirm that SDHC1_DAT[0:3] are pulled high through a 10-20 kΩ resistor to EVDD.

6) please provide U-Boot booting log as textual attachment

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, ufedor

1.QSPI_A_SCK, SDHC2_CLK, SDHC1_CLK, SCAN_MODE_B are all high levels during the power-on reset.

2.SDHC1_DAT[0:3] was pulled to EVDD through a 20K pull-up resistor.

3.ESDHC1 is always 1.8v. Is there any problem with 1.8v during power on?

Note1:

“Though eSDHC1 boots at 3.3V, but it can dynamically switch to 1.8V controlled by the SDHC_VSEL signal.However, for eMMC 1.8V, the IO voltage can be set to 1.8V by default.”

Mentioned In QorIQ LS1012A Reference Manual.

Note1:

“eSDHC1: Supported primarily for SD cards. This is on the EVDD/O2VDD interface. CD/WP/VSEL are at 1.8V. Card initialization happens at 3.3V, but can dynamically switch to 1.8V controlled by the SDHC1_VSEL output pin. No provision to select EVDD=1.8V at boot time.”

Mentioned In AN5192 QorIQ LS1012A Design Checklist - Application Note.

4 Do the SDHC1_VSEL and EVDD_VSEL items in RCW need to be modified?

I will be glad to any advice. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please set SDHC1_VSEL and EVDD_VSEL to 0b00 instead of current 0b01.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, ufedor

U-Boot booting log:

U-Boot 2016.092.0+ga06b209 (Mar 18 2019 - 19:58:17 -0700)

SoC: LS1012A Rev1.0 (0x87040110)

Clock Configuration:

CPU0(A53):1000 MHz

Bus: 250 MHz DDR: 1000 MT/s

Reset Configuration Word (RCW):

00000000: 0800000a 00000000 00000000 00000000

00000010: 35080000 c000000c 40000000 00001800

00000020: 00000000 00000000 00000000 00014571

00000030: 00000000 18c2a120 00000096 00000000

I2C: ready

DRAM: 510 MiB

SEC0: RNG instantiated

PPA Firmware: Version 0.2

Using SERDES1 Protocol: 13576 (0x3508)

MMC: before mmc_initializein mmc_initialize

before mmc_probe

in mmc_probe

uclass_foreach_dev device_probe

in fsl_esdhc_probe

fsl_esdhc_probe addr = 1560000

fsl_esdhc_probe bus_width = 1

fsl_esdhc_probe wp_enable = 0

fsl_esdhc_probe sdhc_clk = 125000000

in fsl_esdhc_init

in mmc_create

mmc_create success

fsl_esdhc_probe fsl_esdhc_init ok

uclass_foreach_dev device_probe

in fsl_esdhc_probe

fsl_esdhc_probe addr = 1580000

fsl_esdhc_probe bus_width = 1

fsl_esdhc_probe wp_enable = 0

fsl_esdhc_probe sdhc_clk = 125000000

in fsl_esdhc_init

in mmc_create

mmc_create success

fsl_esdhc_probe fsl_esdhc_init ok

FSL_SDHC: 0, FSL_SDHC: 1

SF: Detected S25FS512S with page size 256 Bytes, erase size 256 KiB, total 64 MiB

In: serial

Out: serial

Err: serial

Model: LS1012A RDB Board

Board: LS1012ARDB Error reading i2c boot information!

SATA link 0 timeout.

AHCI 0001.0301 32 slots 1 ports 6 Gbps 0x1 impl SATA mode

flags: 64bit ncq pm clo only pmp fbss pio slum part ccc apst

Found 0 device(s).

SCSI: Net: cbus_baseaddr: 0000000004000000, ddr_baseaddr: 0000000083800000, ddr_phys_baseaddr: 03800000

class init complete

tmu init complete

bmu1 init: done

bmu2 init: done

GPI1 init complete

GPI2 init complete

HGPI init complete

hif_tx_desc_init: Tx desc_base: 0000000083e40400, base_pa: 03e40400, desc_count: 64

hif_rx_desc_init: Rx desc base: 0000000083e40000, base_pa: 03e40000, desc_count: 64

HIF tx desc: base_va: 0000000083e40400, base_pa: 03e40400

HIF init complete

bmu1 enabled

bmu2 enabled

pfe_hw_init: done

pfe_firmware_init

pfe_load_elf: no of sections: 13

pfe_firmware_init: class firmware loaded

pfe_load_elf: no of sections: 10

pfe_firmware_init: tmu firmware loaded

PCIe0: pcie@3400000 Root Complex: no link

pfe_eth0, pfe_eth1

Hit any key to stop autoboot: 0

=>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> The waveform of SDHC1_CLK pin is intercepted as follows:

?

> But after power on for about 2.5 minutes, the eMMC worked normally.

> The emmc on the first eSDHC controller can read and write normally

It is required to check POR levels and strapping of all signals having notes 5, 6, 8, 10 in the QorIQ LS1012A Data Sheet, Table 1. Pinout list by bus.

Ensure that TRST_B is pulsed low during the POR sequence.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, ufedor

According to your suggestion, we have made the following check:

1 EMI1_MDC、IIC1_SCL and IIC1_SDA pin is not used,No Connection。

2 According to the datasheet, the rising edge of POR requires 8ns. Our board currently USES MAX6856UK16D3, and the rising edge time is about 50ns。

3 The TRST_B is shorted to the PORESET_B to ensure that it is lowered during the power on.

4 EVDD power supply 1.8v directly

So my questions:

Will the above differences lead to the current problems?

I would appreciate your advices!

Thanks, Diao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What about pins:

62, 127, 71

66

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, ufedor

The waveform of SDHC1_CLK pin has been added to the above。

SDHC2_CLK pin worked normally(1.8 v square wave).

Thank you,

Diao。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please provide U-Boot booting log as textual attachment.