- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Unexpected LPSPI interrupt service

Unexpected LPSPI interrupt service

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Unexpected LPSPI interrupt service

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Tl;DR: The LPSPI ISR is executed three times instead of two times as expected. Normally the first and third ISR calls are expected and the second ISR is unexpected. The unexpected ISR occurs when the LPSPI module is apparently "busy". Sometimes with large number of interrupts, the unexpected LPSPI ISR occurs after the two expected ISRs and it keeps interrupting the CPU until the module is re-initialized.

Background:

The software tools we use are:

S32 Design Studio v1.3

S32K144 SDK RTM 1.0.0

GHS Compiler for ARM

The hardware is a custom application specific board with a 64-pin S32K144 (057U maskset).

Issue Details:

We use LPSPI0 module to communicate with an ASIC at 1Mbps. The MCU is the master and the ASIC is the slave.

Normally, 8bits of data (read command + register address) is sent to the ASIC from the MCU and the ASIC responds with 32 bits of data, all within once chip select low period. This data is then stored in RAM using the DMA. This is repeated every 500us.

After 10 such reads, the DMA ISR is executed where the LPSPI module is configured for 16-bit interrupt-based communication instead of DMA-based communication. 16bits of data is then written to the LPSPI buffer and transmission is started. Once transfer of 16-bits is complete, the LPSPI module calls the ISR (1st expected ISR) in which the LPSPI driver calls a callback function. In the callback, the received data is read (and discarded) and another 16-bits of data is filled in the buffer for transmission. After this second 16-bits are transferred, in the callback from LPSPI driver (2nd expected ISR), the LPSPI module is again configured for DMA-based transfer and the process repeats.

Under normal circumstances, we noticed that the LPSPI ISR is being executed thrice, two of which is expected as described above and one execution is unexpected. During the unexpected ISR execution only MBF in Status Register of LPSPI0 is set. There are 2 words in the TX Buffer as expected and no error flags are set.

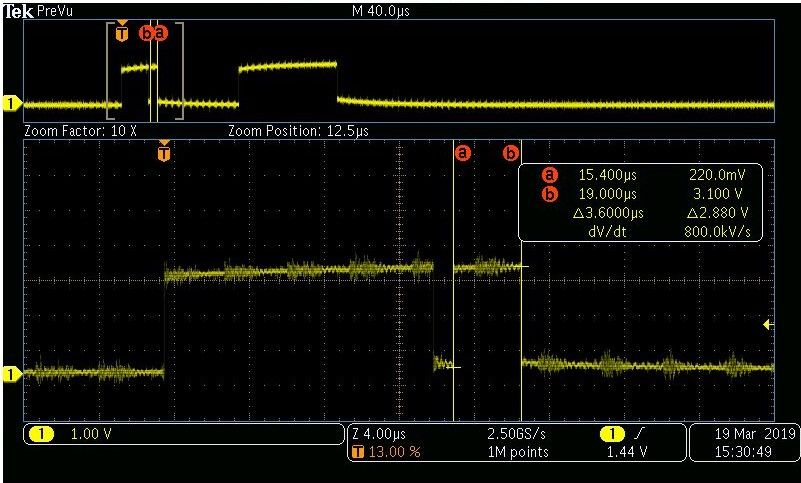

A visualization of the interrupt execution times is in the below image.

A port pin was made high when the ISR execution began and made low before returning from the ISR.

The upper section of the image shows the three ISR executions while the lower section of the image is zoomed into the first two ISRs.

Gap between the first and second ISR is 1us.

We originally found the issue when testing the system under high CAN interrupt load.

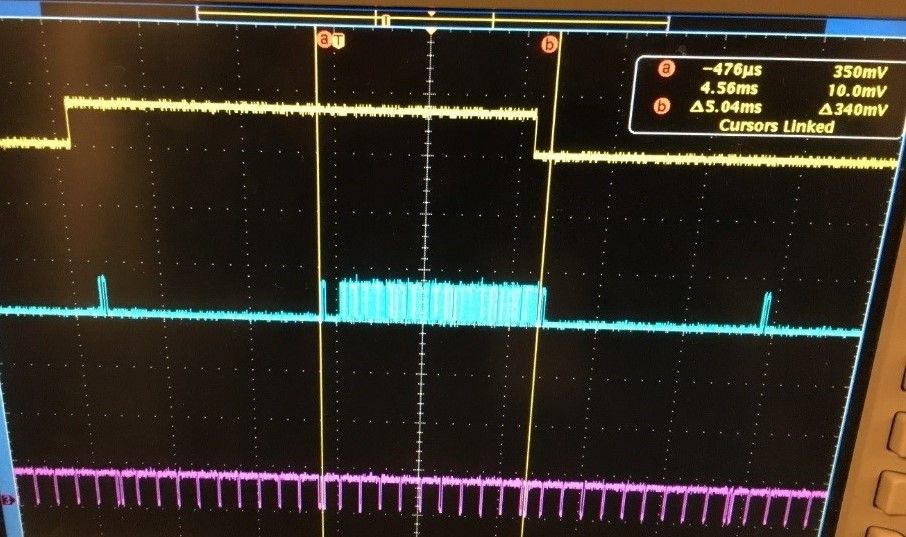

We found that if there are a large number of CAN interrupts, sometimes this unexpected LPSPI interrupt occurs after the second expected LPSPI interrupt. But for some unknown reason the LPSPI module keeps interrupting the CPU from then onwards until the module is reconfigured. This is visualized in the image below.

The yellow signal on top is a port pin toggled every 10ms.

The blue signal in the middle is the execution of the LPSPI0 ISR.

The pink signal is the Chip select line of LPSPI0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share your project?

Did you tried to run this application based on our last release? RTM 3.0.0?

Best regards,

Razvan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Razvan,

I am sorry, but the project source code is confidential and cannot be shared.

I am working to get a minimal set of source code that can reproduce the issue. I will share it as soon as it is available.

Unfortunately, migrating our source code to use RTM 3.0 of the SDK will be a huge task. So we want to find the issue with the current code.

With Best Regards,

Sahyadri