- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Possible incosistence into MPC5777C Reference Manual (Chapter 39 - IGF / Falling threshold register)

Possible incosistence into MPC5777C Reference Manual (Chapter 39 - IGF / Falling threshold register)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Possible incosistence into MPC5777C Reference Manual (Chapter 39 - IGF / Falling threshold register)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

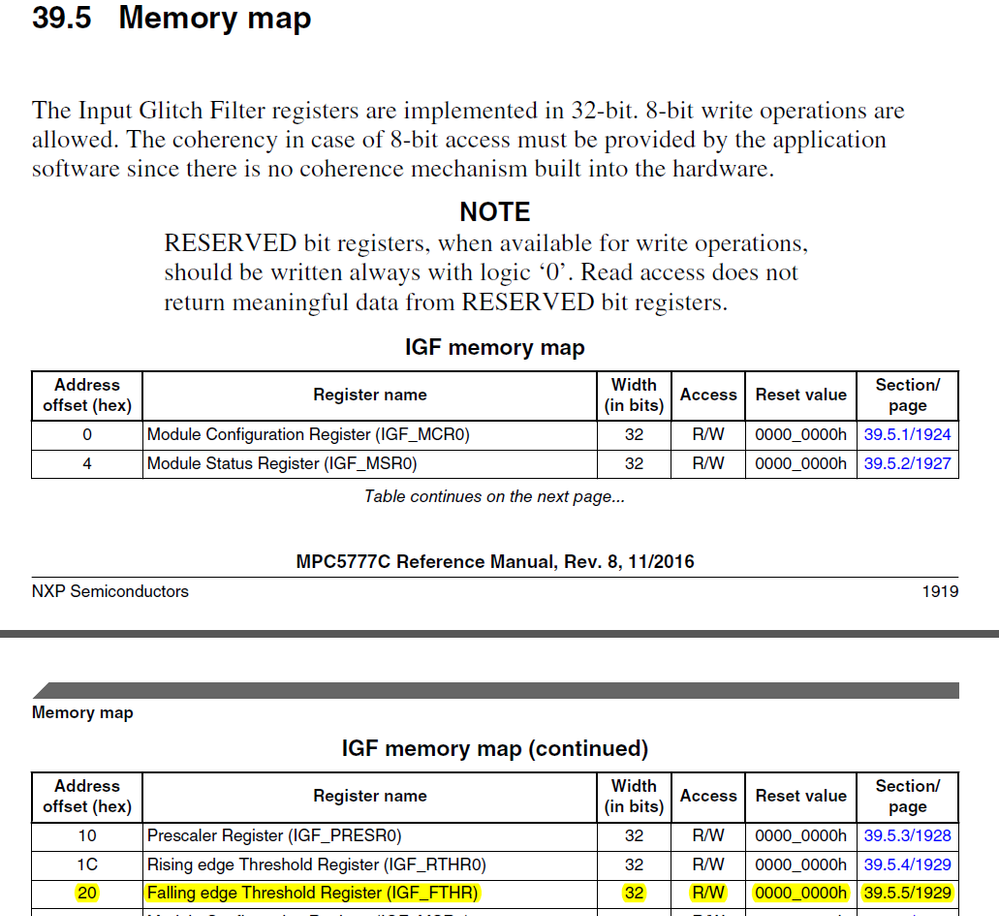

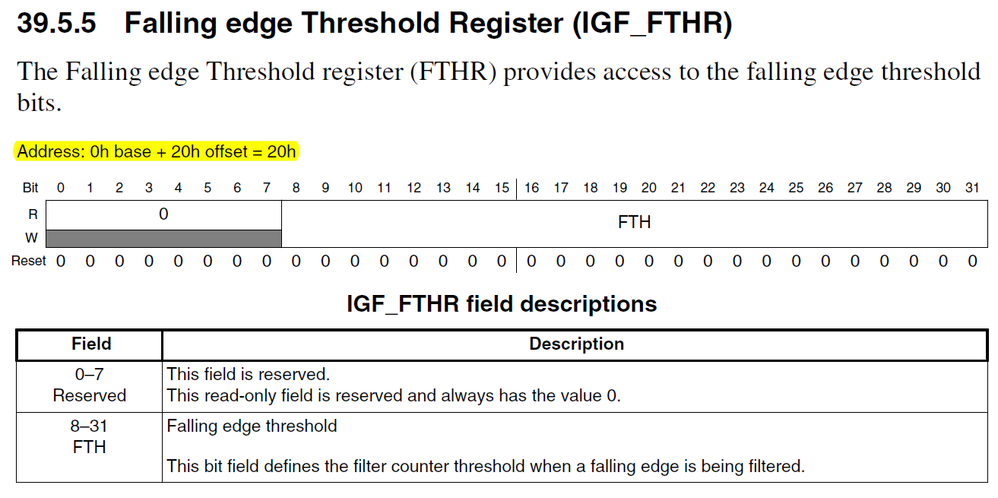

Trying Input Glitch Filter (IGF), of MPC577C, it looks like each the IGF's channels has its own IGF_FTHR register;

whereas MPC5777C Reference Manual (Document Number: MPC5777CRM / Rev. 8.1, 09/2018 - Chapter 39

Input Glitch Filter (IGF)), defines only one IGF_FTHR register per each IGF module (IGF_0 or IGF_1), see yellow marked text into below extracts from reference manual.

I didn't find any related "errata", so I ask if really all IGF channels have proper IGF_FTHR (should be IGF_FTHRn) register located at the address 0h base + 20h offset + (64d x i), where i=0d to 45d ?

And consequently the Reference Manual should be corrected?

Thank you,

Enrico Ferrari

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

many thanks for your clarifications/confirmations.

Best Regards,

Enrico Ferrari

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Enrico,

yes, this is inconsistency in the RM. The Falling edge threshold register exist for each channel just like Rising edge threshold register.

Falling edge threshold register address can be calculated as "Address: 0h base + 20h offset + (64d × i), where i=0d to 45d"

The RM needs to be updated to include a Ffalling threshold register for each channel. There has already been a docs ticket submitted about this.

BR, Petr