- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K144 PDB ADC DMA

S32K144 PDB ADC DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 PDB ADC DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

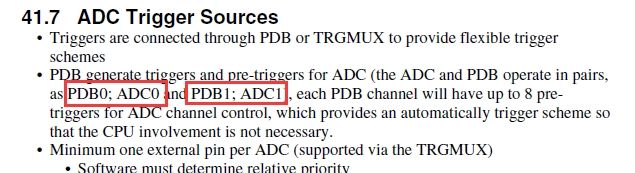

My current problem is: I can use the two channels of PDB1 (CH0\CH1) for triggering, CH0 can trigger for 8 ADC channels, but CH1 channel only triggers one channel. Please help analyze, thank you!

Application scenario: Based on our circuit design. At present, we use 12 channels of ADC1 (the ADC model we selected has only 12 channels).

For the understanding of this part of the manual:

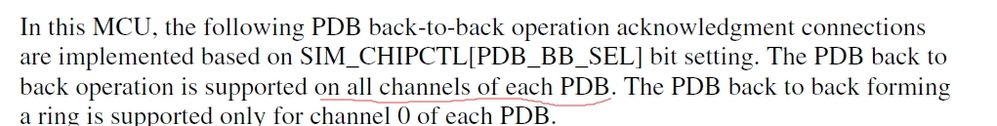

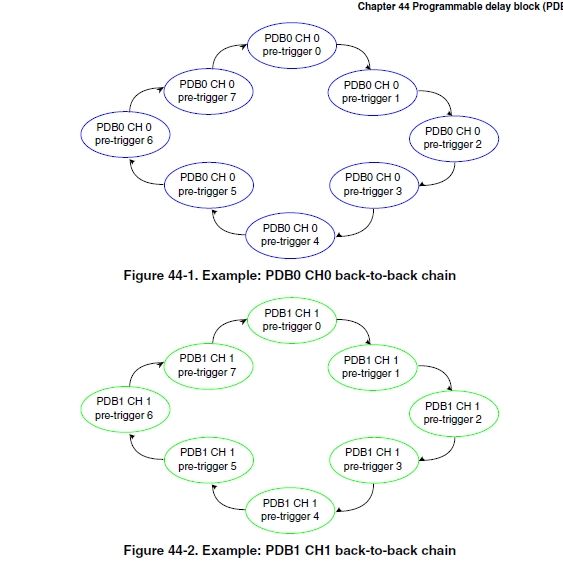

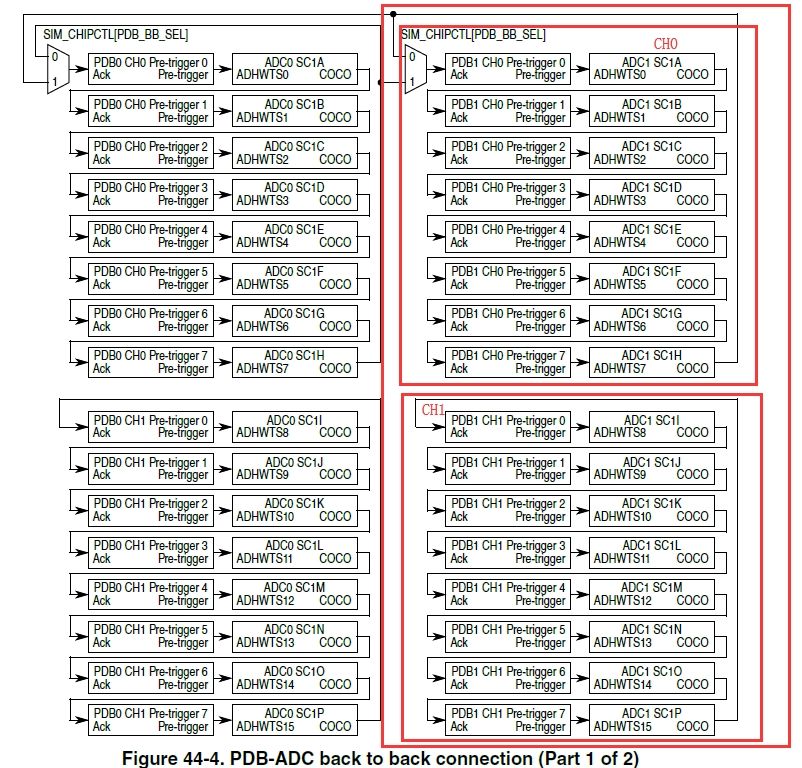

1. BACK TO BACK mode is supported on all channels. As shown below

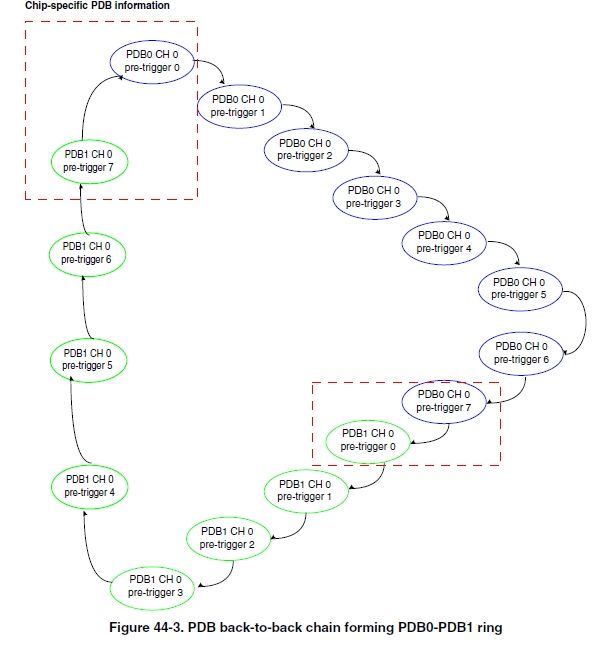

2. There are two BACK TO BACK modes, and the mode selection is selected by SIM_CHIPCTL[PDB_BB_SEL].

2.1 When the first SIM_CHIPCTL[PDB_BB_SEL]=0. There is no direct connection between PDB0 and PDB1 (PDB0CH0, PDB1CH0), that is, the 8 pre-trigger channels of CH0 of PDB0 form a loop in sequence, and the 8 pre-trigger channels of CH0 of PDB1 form a loop to trigger in sequence.

2.2 When the second SIM_CHIPCTL[PDB_BB_SEL]=1. PDB0 and PDB1 form a large loopback (PDB0CH0-PDB1CH0), that is, the CH0 pre-trigger of PDB1 is completed after 8 pre-triggers of CH0 of PDB0 are completed.

3. Application analysis

Combined with our application field shadow (only 12 channels of ADC1 are used), we only use PDB1, as shown below

Combine the picture below,

So, we SIM_CHIPCTL[PDB_BB_SEL]=0, the first method in Section 2, to fulfill our requirements (this method applies to the S32K144 demand sent yesterday).

In my program, I set the delay trigger value of the channel (guarante the value of the CH1 channel of PDB1 is later than the trigger time of the CH0 channel of PDB1) to realize the two channels triggering the two PDB1 in the counting period of one PDB. Channels (CH0\CH1).

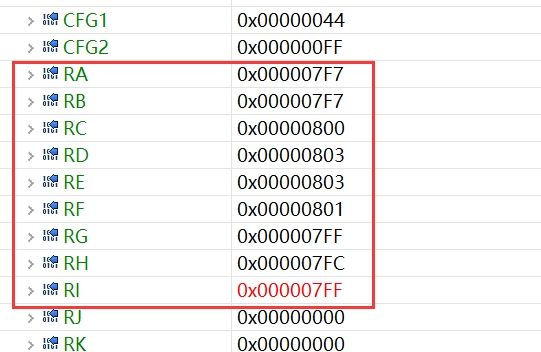

During the debugging process, the trigger of the ninth channel is realized, as shown in the figure below.

Where RI is triggered by the CH1 channel of PDB1.

The current problem is that, according to the above analysis, if the PDB1 CH1 count can trigger the RI channel, it should be able to simultaneously trigger the 8-channel pre-trigger channel corresponding to CH1 (because PDB1 CH0 triggers 8 ADC channels at the same time), but Now only RI has implemented sampling.

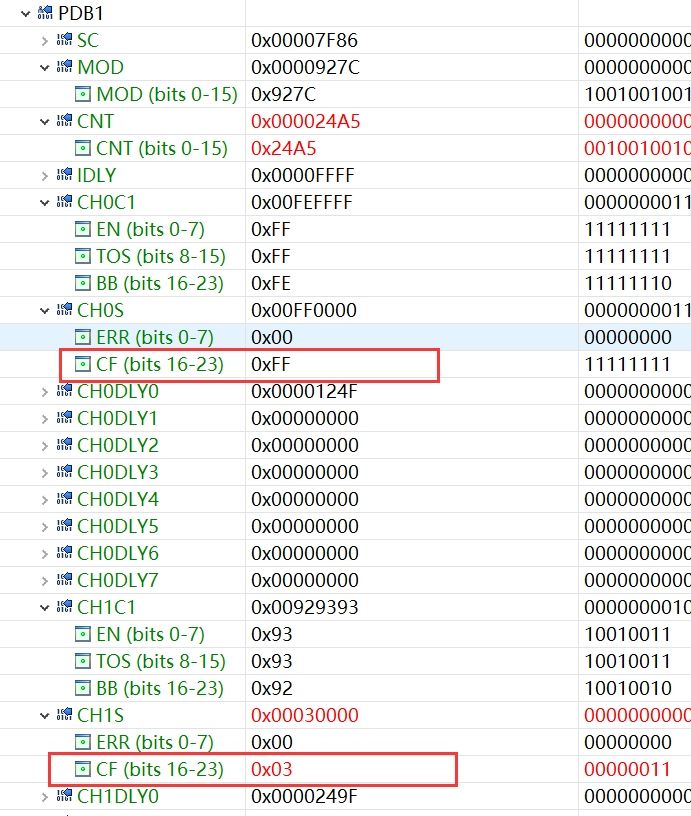

I have read the PDB chapter of the reference manual in detail today. The conclusion is that when the PDB COUNTER counts, it is repeatedly compared with the delay setting value PDBCHnDLYm. When it is equal to this value, the corresponding pre-trigger channel corresponding to PDB1 CH1 is triggered to sample the ADC channel. If the corresponding delay setting value PDBCHnDLYm is reached, the bit corresponding to CF will be set. I intercepted the state of the relevant register of PDB1 during operation. The CF bit of CH0 of PDB1 is all ones, but the CF bit of CH1 channel of PDB1 is not all ones. There was no problem with the difference before the end.

Above, trouble to help analyze the problem, thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

back-to-back connection between pre-triggers is given, as Figure 44-4 shows. Thus only adjacent pre-triggers can form such connection. You cannot enable BB bit on pre-triggers 1, 4 and 7, the acknowledgement will not work.

In your case only pre-triggers 0 and 1 was generated, indicated by CF bits and ADC channel 8 (SC1I) and 9 (SC1J) should be converted, if those channels are enabled in ADC1.

BR, Petr