- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC11Cxx SPI Master - Slave

LPC11Cxx SPI Master - Slave

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC11Cxx SPI Master - Slave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There were lot of questions/answers on this topic. None of them helped resolving my issue though ..

I have one 11Cxx as a master and another 11Cxx as a slave.

I tapped into SPI lines with logic analyzer and I can clearly see the transfer of the data from Master to slave. With write and "read" requests. I am sending one byte as an address and one byte as a data. And for reading is 1 byte 0x01 and 0xff for data. (expecting response for that byte). "Chip select" is a custom pin (internal pull up mode). It is actually connected to physical SSEL, but running in GPIO func and controlled by software. I can see it on logic analyzer that its pulling low before the clock and data, and pulling high after data transfer.

I lowered the speed of SPI to get this thing working, so I am using 400kHz config, confirmed with scope.

Slave SSEL is configured as a normal SSEL with pull up mode.

Master is fully happy with that, no interrupts pending there, no busy flags, all fine.

Slave on the other hand is having all sort of problems there. My interrupts on "RX not empty" and "TX not empty" kicked in immediately after initialization of the SPI. And after that SPI get stuck with BSY flag constantly on. No further interrupt happen on slave, even though logic analyzer is showing data.

What should happen when master pulls the select line down and sends the byte of data ?

Will Slave receives that as "RX not empty" interrupt?

How does slave knows it is reading time? Is it just an "agreement", when this byte is received, return data from slave ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sven Savic,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1)What should happen when master pulls the select line down and sends the byte of data?

-- At this point, the slave device should be ready to receive.

2) Will Slave receives that as "RX not empty" interrupt?

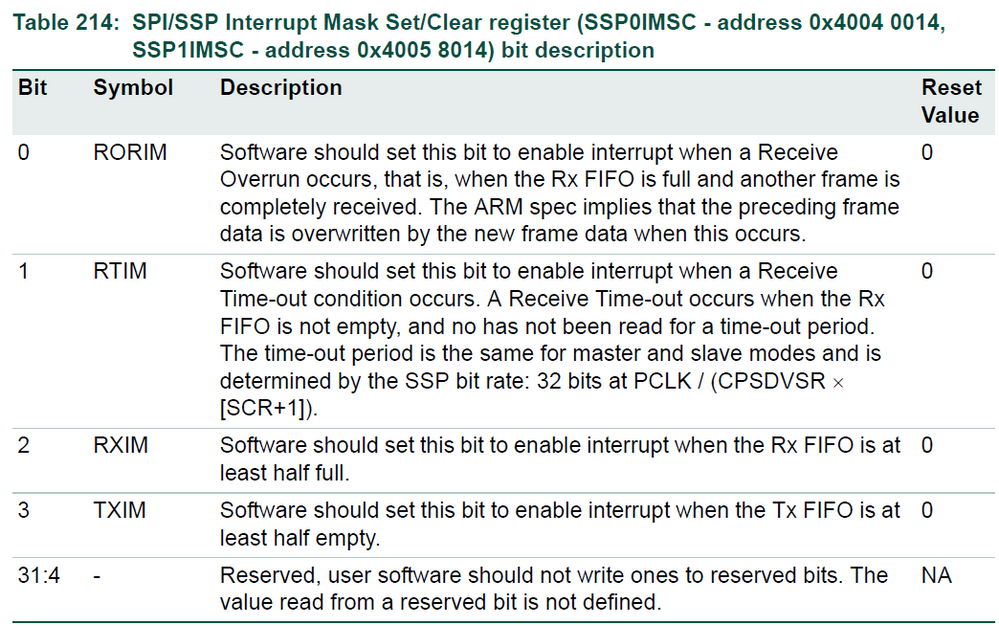

-- Actually, I don't find the "RX not empty" interrupt in the Interrupt Mask Set/Clear Register, whether you can clarify it.

3) How does slave know it is reading time? Is it just an "agreement", when this byte is received, return data from the slave?

--It's determined by the SPI protocol.

I've also attached an SPI demo to test both SSP master and slave mode on the LPC11xx MCU, please refer to it for details.

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had some time to "play" with this. While code for master is working fine, slave is working only if I poll the status bit and react on the status. I can read value back from the master. Writing seems to be more tricky as I am not sure whether I need to read the dummy value from buffer to clear the interrupt status or just throw the value to DR.

This approach is not preferable, as I need to waste cycle time checking whether there is something in the RX buffer. And I can easily hit the timeout if I do some other tasks.

Enabling interrupts just ends with getting overruns. I cant seem to clear the overrun with writing to ICR. My interrupt just gets called again in next cycle. So, basically I get stuck in interrupt deadlock. Thats my original issue explained in the original question.

Why is writing to ICR not clearing overrun interrupt ? Do I need to read from DR even though I got timed out to clear the interrupt ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

Will Slave receives that as "RX not empty" interrupt?

-- Actually, I don't find the "RX not empty" interrupt in the Interrupt Mask Set/Clear Register, whether you can clarify it.

I was referring to RXIM interrupt.

Thanks for the demo, I didnt yet have the time to check it out.