- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- T1024 RCW and DDR Validation Doubts

T1024 RCW and DDR Validation Doubts

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

T1024 RCW and DDR Validation Doubts

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

I have designed a custom board based on T1024RDB. I have few doubts:

Doubt-1: In T1024RDB, When select switch settings to load RCW from SPI flash (nand flash and nor flash is blank), i notice that RCW in register DCFG_CCR_RCWSR1 is different from the data in binary file. Why it is different, it should be same as that in binary file or in .txt file which override RCW

Doubt-2: Doubt-2: In T1024RDB, If i write NAND flash with u-boot image (spi and nor flash blank), u-boot do not run at all. I configured switch settings accordingly. What can be the reason ?

Doubt-3: Can i load RCW and run u-boot from nand flash (without using nor and spi flash) ? The NAND flash used in T1024RDB is MT29F8G08ABBCAH4 . This flash is 8-bit, 4096 blocks (2 planes), 64 page/block, page size 4KB. But this option is absent in QCVS field IFC_Mode and also in reference manual of T1024, Page-190. Which option should i select. Nearest option provided is 8-bit NAND Flash, 4 KB page, 128 pages/block (64page.block is absent).

Doubt-4: In T1024RDB, i configured switch settings for SPI flash (when nand flash and nor flash is blank) , some RCW is being loaded. I checked RCW from registered through CodeWarrior in Connect Mode. Now if i run ddr validation tool from QCVS project, it fails. Why it is failing ?

Doubt-5: Should DDR Validation work if i write only 64 byte RCW with preamble (8 bytes) and CRC , PBL.bin file generated by QCVS tool without any PBI command and not boot code? Should i put both cores in hold-off state or core-0 in non-holdoff state ?

I hope to get answers to solve my issues. Thank you all in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Please provide (attach as text file) U-Boot booting log. Explain why you mentioned RCW override - is it used?

2) Which exactly image is in question? How the image is written to the NAND Flash? Please dump the NAND Flash contents in U-Boot (block 0) and attach the log as text file.

3) Yes.

You wrote:

> Nearest option provided is 8-bit NAND Flash, 4 KB page, 128 pages/block

This is OK. It is possible to use cfg_rcw_src=1_0001_0101 (8-bit NAND Flash, 4 KB page, 128 pages/block), in U-Boot it is required to specify correct block size - 64 pages.

4) Is U-Boot capable to boot? Please attach the boot log as text file.

Please capture the DDR Tool error message screenshot.

5) It is reasonable to use RCW provided in the SDK pre-built image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Ufedor,

Thank you for your reply. I am using Code-warrior and QCVS for the first time. Kindly note below reply:

1) Below were my step by step actions:

(a) In T1024RDB, Uboot was loaded from SPI (uboot log is attached).

(b) After that I connected CW-TAP using Connect mode and added T1024RDB_RCW_1200_400_1600.txt (file attached).

(c) I checked value of register DCFG_CCSR_RCWSR1 = 0x080a000a . (Screenshot is attached: Debug_Connect_AfterSPI_Boot.jpg). Note that In 1024RDB_RCW_1200_400_1600.txt it is 0x0810000c.

Why was it 0x080a000a and not 0x0810000c ?

2) In T1024RDB, If i write NAND flash using Codewarrior Target_Task. Image name is "u-boot-nand-T1024RDB_NAND-2014.07+fslgit-r0.bin" File attached. (I got this image file with Reference design board Pen drive).

Also, I erased SPI flash and NOR flash.

Now RDB do not boot at all. There is nothing on serial console. what can be the reason ?

3) OK. But I cannot boot from NAND flash because of the reason given in above point-2

4) I write uboot image into spi flash (Attached uboot image file : u-boot-spi-T1024RDB_SPIFLASH-2014.07+fslgit-r0.bin) & changed switch settings to boot from SPI.

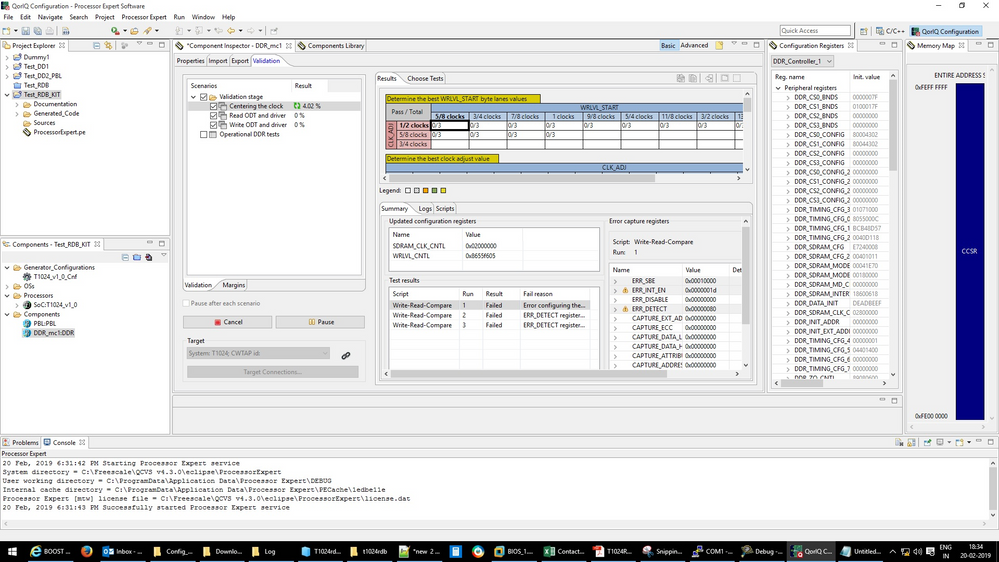

After this Uboot was capable to boot from SPI flash. Then I run DDR validation tool from QCVS software. I failed. Refer attached log file "QCVS_DDRvalidationFail_Log.txt" and screenshot "QCVS_DDRV_Fail_log.jpg"

What can be the reason ?

5) Will DDR validation work if i write only RCW in SPI flash and not complete uboot ?

Because I want to run DDR validation tool for my custom board for which i don't have uboot right now. After testing DDR, i will generate uboot for my custom board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please find answers inline.

1) Below were my step by step actions:

(a) In T1024RDB, Uboot was loaded from SPI (uboot log is attached).

(b) After that I connected CW-TAP using Connect mode and added T1024RDB_RCW_1200_400_1600.txt (file attached).

No need to add the TXT file (and perform the RCW override) when valid RCW is present in the RCW source ROM.

Remove the TXT file and re-check.

(c) I checked value of register DCFG_CCSR_RCWSR1 = 0x080a000a . (Screenshot is attached: Debug_Connect_AfterSPI_Boot.jpg). Note that In 1024RDB_RCW_1200_400_1600.txt it is 0x0810000c.

Why was it 0x080a000a and not 0x0810000c ?

2) In T1024RDB, If i write NAND flash using Codewarrior Target_Task. Image name is "u-boot-nand-T1024RDB_NAND-2014.07+fslgit-r0.bin" File attached. (I got this image file with Reference design board Pen drive).

Also, I erased SPI flash and NOR flash.

Now RDB do not boot at all. There is nothing on serial console. what can be the reason ?

Excuse me, how the board could boot if you erased U-Boot from the SPI Flash?

Use hard coded RCW source option and re-program SPI Flash and/or NOR Flash.

3) OK. But I cannot boot from NAND flash because of the reason given in above point-2

See 2)

4) I write uboot image into spi flash (Attached uboot image file : u-boot-spi-T1024RDB_SPIFLASH-2014.07+fslgit-r0.bin) & changed switch settings to boot from SPI.

After this Uboot was capable to boot from SPI flash. Then I run DDR validation tool from QCVS software. I failed. Refer attached log file "QCVS_DDRvalidationFail_Log.txt" and screenshot "QCVS_DDRV_Fail_log.jpg"

What can be the reason ?

How the DDR Tool was initialized?

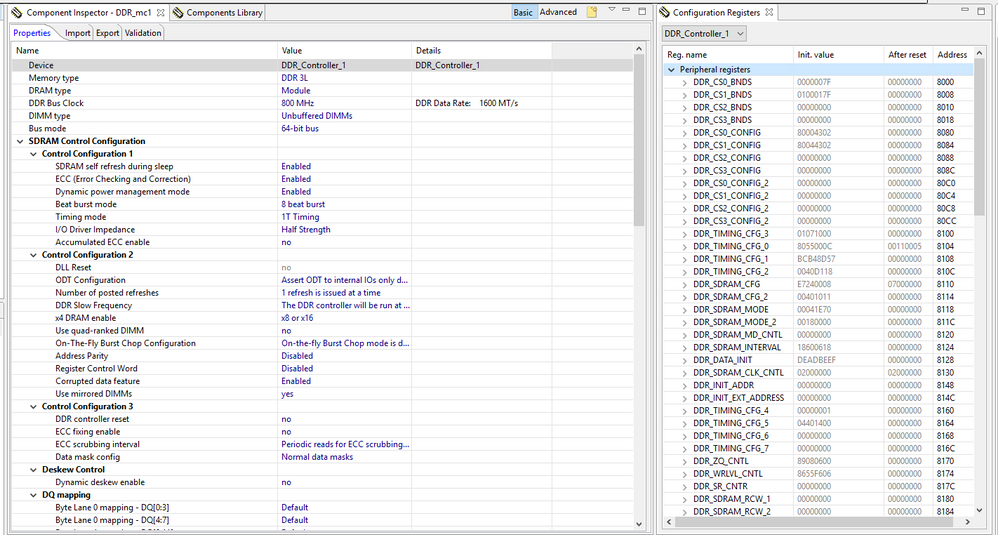

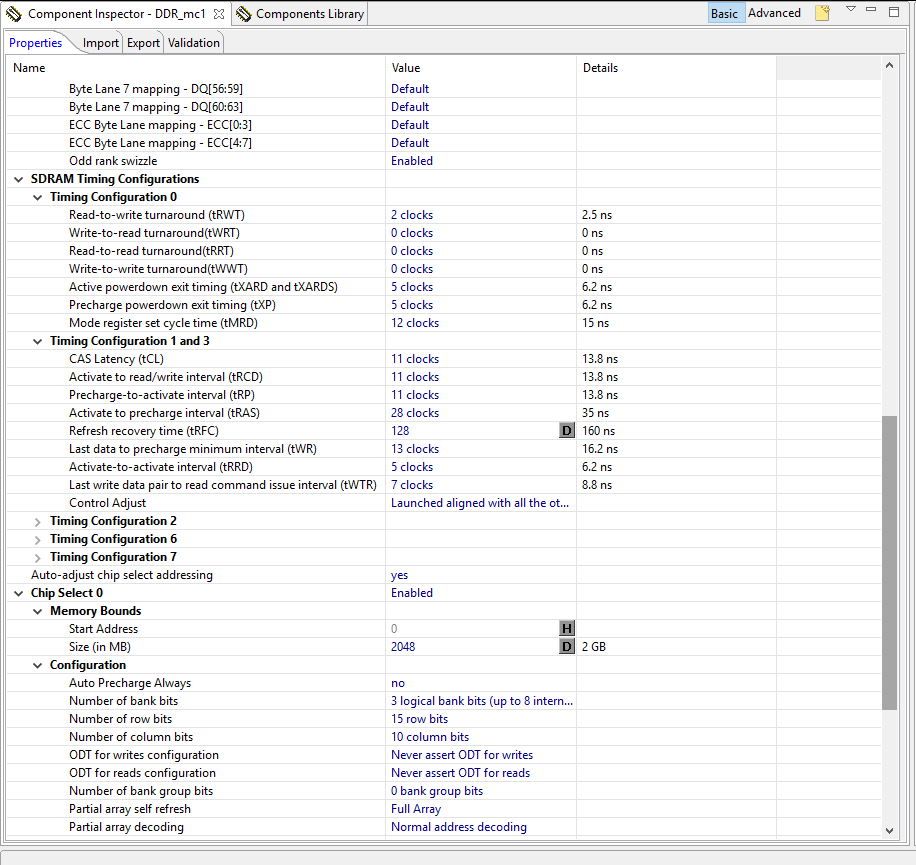

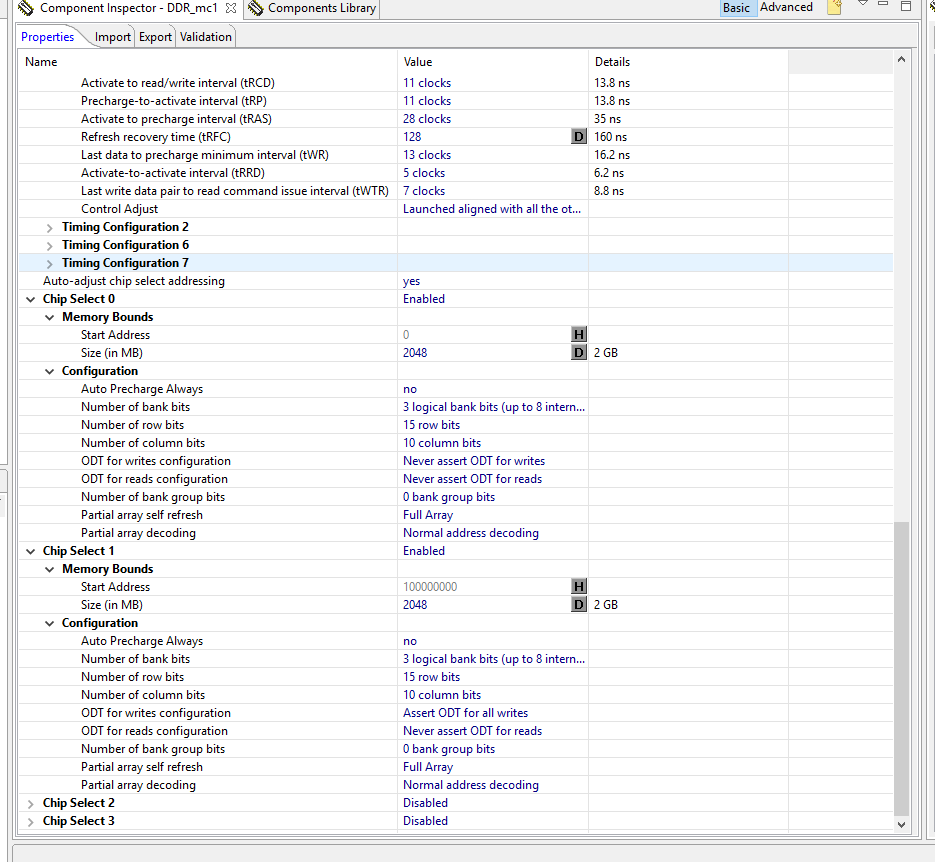

Please provide screenshot of the DDR configuration pane - refer to the QCVS DDR Tool User Guide, Rev. 4.x, Figure 2. DDR configuration for DRAM module.

5) Will DDR validation work if i write only RCW in SPI flash and not complete uboot ?

Because I want to run DDR validation tool for my custom board for which i don't have uboot right now. After testing DDR, i will generate uboot for my custom board.

Yes, it will.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Ufedor,

Thank you very much for prompt response. Kindly help me little more....

1) Solved: Earlier, I was not able to run debug configuration in connect mode without giving .txt file (required for JTAG override). I updated Codewarrior. Now I can connect to CW-TAP in connect mode without giving .txt file. Now values of DCFG_CCSR_RCWSRn are exactly same as provided in flash memory. Hence, it is solved.

2) I erased both SPI flash & NOR flash and written uboot in NAND flash "u-boot-nand-T1024RDB_NAND-2014.07+fslgit-r0.bin". Can you please tell below:

(a) What is the reason booting of uboot is not possible from NAND flash ?

(b) Can I load RCW+PBI from NAND flash and cannot boot from NAND flash ?

3) Same as 2)

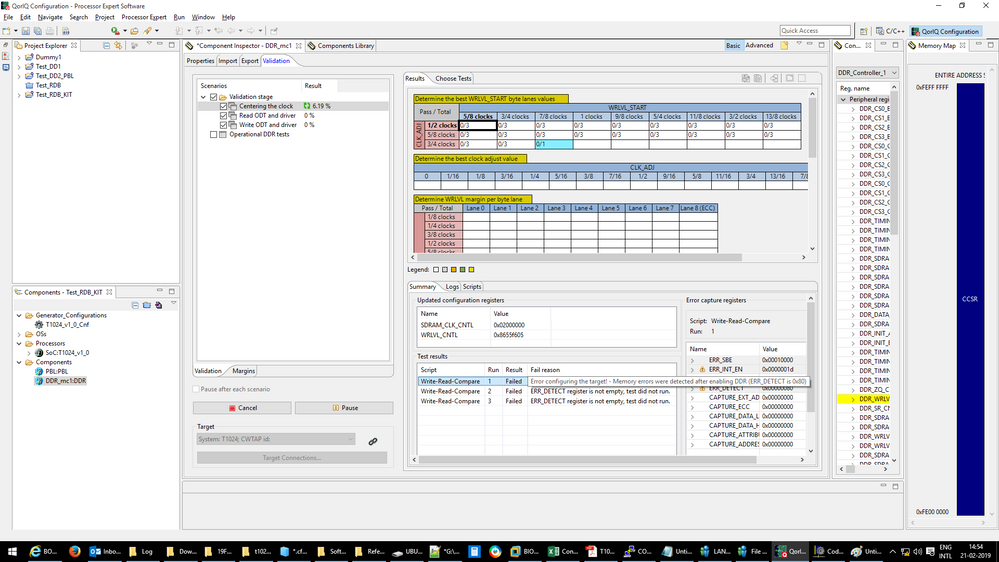

4) Please find below screenshot. I am first trying DD validation on T1024RDB. But it fails. I got configuration by reading SPD.

5) ok.

Thanks & Regards,

Abhishek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

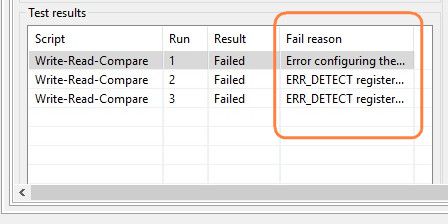

Please expand (or just copy) the statements from the "Final reason":

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

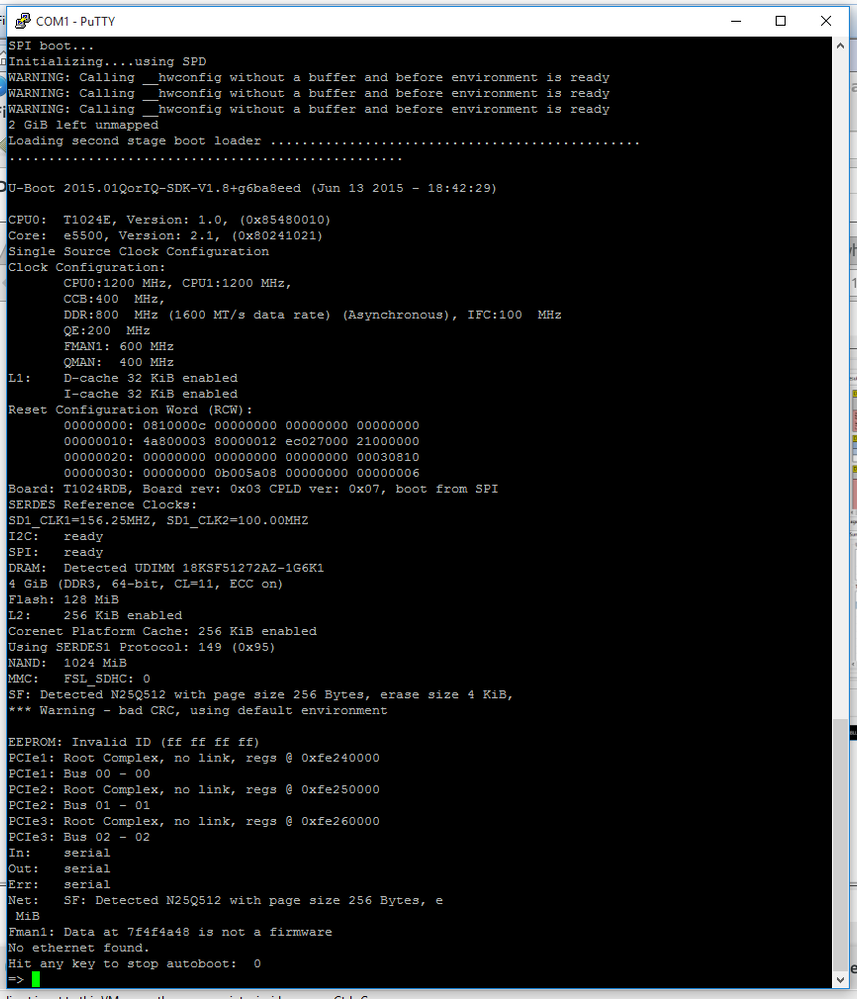

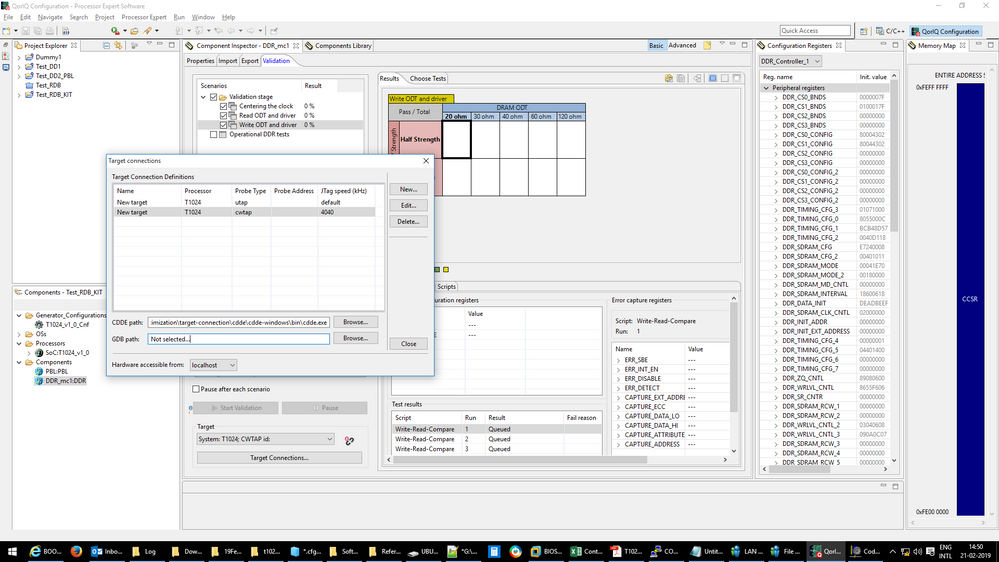

Dear Ufedor,

Refer below screenshot:

- After T1024RDB power-on, uboot console

- Settings of CW-TAP before running DDR-v tool

- Result while running DDR-V tool

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you tried to "Import from target" when U-Boot is running?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hii Ufedor,

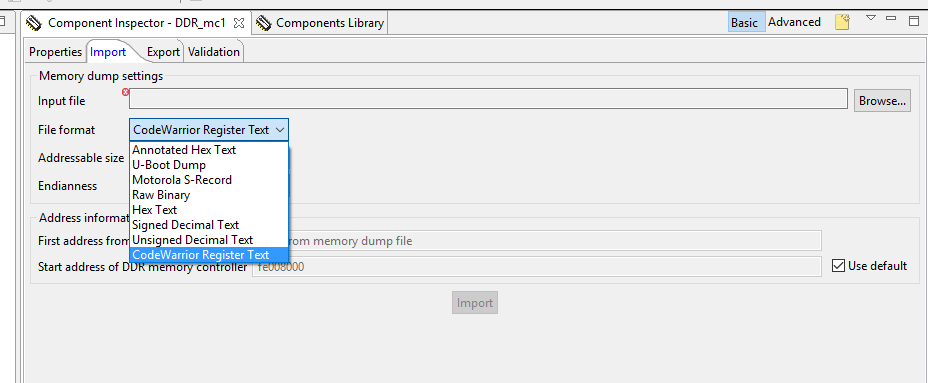

No, Import failed. Can you please guide me, how to "import from target" .

- Which option to use for file format?

- How to get input file from uboot. Should I use "md" command ? What is the address range to get ddr settings in uboot?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To perform import from target refer to the QCVS DDR Tool User Guide, Figure 2. DDR configuration for DRAM module:

"Configuration mode" -> select "Import from target".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Ufedor,

DDR-3 Validation has been passed. Configuration was imported from U-boot Dump.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

2) I erased both SPI flash & NOR flash and written uboot in NAND flash "u-boot-nand-T1024RDB_NAND-2014.07+fslgit-r0.bin". Can you please tell below:

(a) What is the reason booting of uboot is not possible from NAND flash ?

Which cfg_rcw_src is used?

(b) Can I load RCW+PBI from NAND flash and cannot boot from NAND flash ?

Only if the NAND Flash was programmed incorrectly.

4) What is the cfg_rcw_src value when DDR Tool is running?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear ufedor,

2) I erased both SPI flash & NOR flash and written uboot in NAND flash "u-boot-nand-T1024RDB_NAND-2014.07+fslgit-r0.bin". Can you please tell below:

(a) What is the reason booting of uboot is not possible from NAND flash ?

Which cfg_rcw_src is used?

I tried with both : cfg_rcw_src = 1_0001_0101 and cfg_rcw_src = 1_0001_0001

(b) Can I load RCW+PBI from NAND flash and cannot boot from NAND flash ?

Only if the NAND Flash was programmed incorrectly.

Is it possible to load only RCW with zero PBI commands (Only RCW without PBI commands) and run DDR-Validation tool ?

4) Please try to boot the board into U-Boot and during DDR Tool initialization use option "Import from target".

Can you please guide me, how to "import from target" .

- Which option to use for file format?

- How to get input file from uboot.

- Right now I am booting from SPI flash. Should I use "md" command ? What are the address range to import ddr settings?

Please also tell me, What are the address range to import RCW with PBI and which file format to use?

Thanks.

Thanks & Regards,

Abhishek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

4) What is the cfg_rcw_src value when DDR Tool is running?

To perform import from target refer to the QCVS DDR Tool User Guide, Figure 2. DDR configuration for DRAM module