- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Vybrid VF50 BootROM fuse bank CRC checking

Vybrid VF50 BootROM fuse bank CRC checking

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Vybrid VF50 BootROM fuse bank CRC checking

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we use SoC module Colibry VF50 produced by Toradex - module contains VF50 MPU, a NAND flash and a DDR3 ram.

With original configuration from Toradex the MPU works properly. Original configuration uses ext.oscilator ( i.e. OSC_BYPASS fuse is not blown ).

Problem is that when an ext.oscilator clock failure occurs ( just temporary failure ) then MPU freeze forever ( testing can be done in u-boot ). So we configured the MPU to reset it when FOSC is less than 40MHz - register SRC_SICR[CMU_OLR]. It works as expected, but we have another issue.

When MPU resets and ext.oscilator is not working properly BootRom enters into safe fail mode - serial download ( ref.manual 7.5.4.3 Clocks at Boot Time ).

We intended to avoid this with blowing of OSC_BYPASS fuse. After the OSC_BYPASS fuse is blown, the MPU after reset / power up always enters to serial download mode immediately and we have no idea why.

Could problem be that we modified only OSC_BYPASS fuse and didn't modify CRC for given fuse bank? Does the VF50 BootROM do checking of the fuse bank CRC?

When BootROM decides to enter fail safe mode ( serial download ) - is the failure reason stored as an error code in a register - to have possibility to get it and analyze it?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- we configured the MPU to reset it when FOSC is less than 40MHz - register SRC_SICR[CMU_OLR]. It works as expected

I think you refer to CMU_OLR bit description on page 850 VFxxx RM Rev.0 10/2016:

- Configures CMU event of FOSC frequency less than 40 Mhz

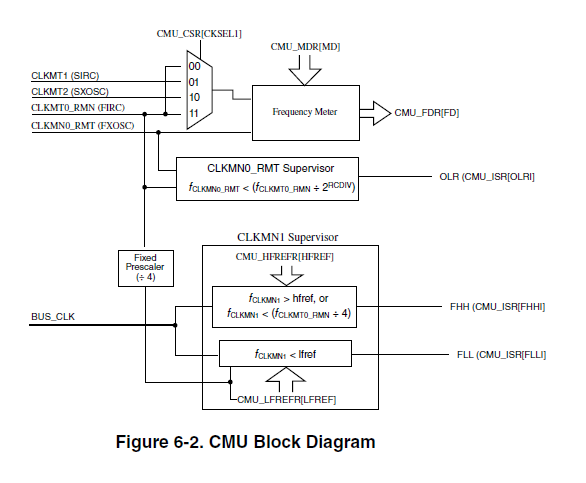

This must be wrong and rudiment from older manual perhaps for different chip. First of all oscillator clock is 24MHz on Toradex, so how would it help comparing to 40MHz? It is also contrary to Figure 6-2. CMU Block Diagram:

As you may see OLRI compares internal 24MHz oscillator (FIRC) to external oscillator (FXOSC), which is 24MHz for Toradex module. 2^RCDIV is 1,2,3 or 4. So in the best case you can compare external FXOSC (24MHz) to FIRC/2 (12MHz). (BTW did you enable clock monitor? OLRI, FHHI and FLLI don’t work without enabling CMU). 24 vs 12MHz is a big frequency step! Since all apps operate at high PLL clocks, also PLLs with removed source clock usually operate for a while until going totally into the weeds, I think you should compare bus clock to internal/external oscillator. Comparison borders should be set quite narrow. As soon PLL and bus clock drifts, reset using SRC_SIRC or fire interrupt on failure to switch in ISR immediately back to internal oscillator and try to recover.

Edward