- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- MASTER_RST and PERIPH_RST on LPC1853

MASTER_RST and PERIPH_RST on LPC1853

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MASTER_RST and PERIPH_RST on LPC1853

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have observed different behavior between LPC1853 MCUs built in different years. They are all revision 'A'. I will list two MCUs here for comparison:

1) LPC1853FET256 ESD15300A

2) LPC1853FET256 ESD17010A

The first one was manufactured in 2015 week 30, and the second one in 2017 week 1. The difference in behavior is with regards to GPIO P5_3 (T8). There might be other GPIO that is affected, but I am focusing on this pin for this discussion. On the first MCU, when LPC_RGU->RESET_CTRL0's bit 1 (PERIPH_RST) is set, T8 is not affected. On the second MCU, when LPC_RGU->RESET_CTRL0's bit 1 is set, T8 is pulled low by the MCU.

Looking at the errata (ES_LPC185X_3X_2X_1X_FLASH) for this MCU, RESET.2 states this:

Problem:

On the LPC18xx, PERIPH_RST is not functional. CMSIS call NVIC_SystemReset() uses

PERIPH_RST internally and is also non-functional.

Work-around:

There is no work-around. To reset the entire chip, use the CORE_RST instead of using

CMSIS call NVIC_SystemReset() or PERIPH_RST.

My first question is:

What does 'not functional' mean? I could see the MCU reset when PERIPH_RST is set. There is a difference in behavior depending on the manufacture date though.

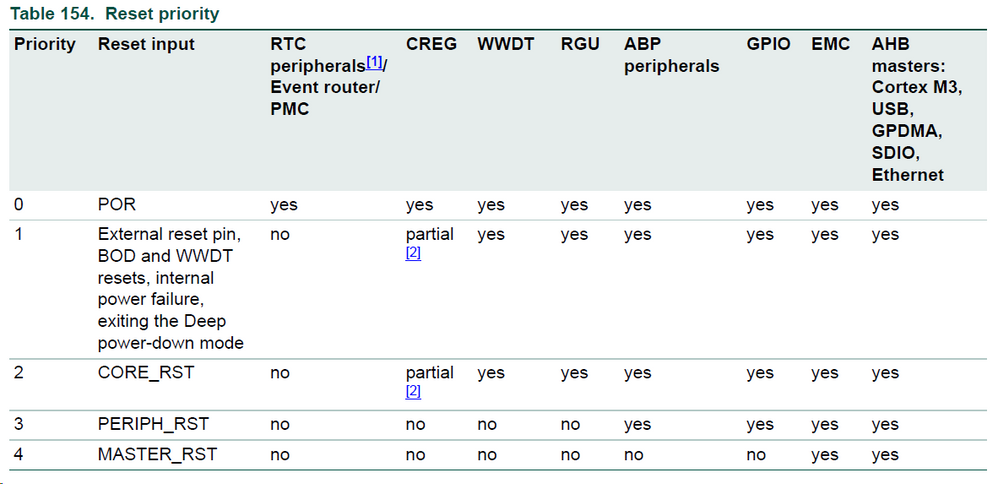

Here is Table 154 from UM10430:

My second question:

If I do not want any GPIO to change state during MCU reset, could I use MASTER_RST?

The errata (RESET.1) also says to not use it:

Problem:

On the LPC18xx, MASTER_RST and M3_RST are not functional.

Work-around:

There is no work-around. To reset the entire chip use the CORE_RST instead of using

MASTER_RST or M3_RST.

My third question: Is PERIPH_RST or MASTER_RST safe to use in any revision 'A' LPC1853?

RESET.1 in the errata also says MASTER_RST is not functional. I hope someone could help clarify what this means, as I observed the MCU reset without changing the state of T8 when MASTER_RST is used on both the above MCUs.

Any help would be greatly appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rex Lam,

I understand that you might be seen this behavior for this MCU, but we can't assure that this behavior will always be present and how long will it last.

Sorry for the inconvenience this might cause you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply Alexis. I appreciate the information.