- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5644A hardware interrupt mode can not run

MPC5644A hardware interrupt mode can not run

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5644A hardware interrupt mode can not run

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

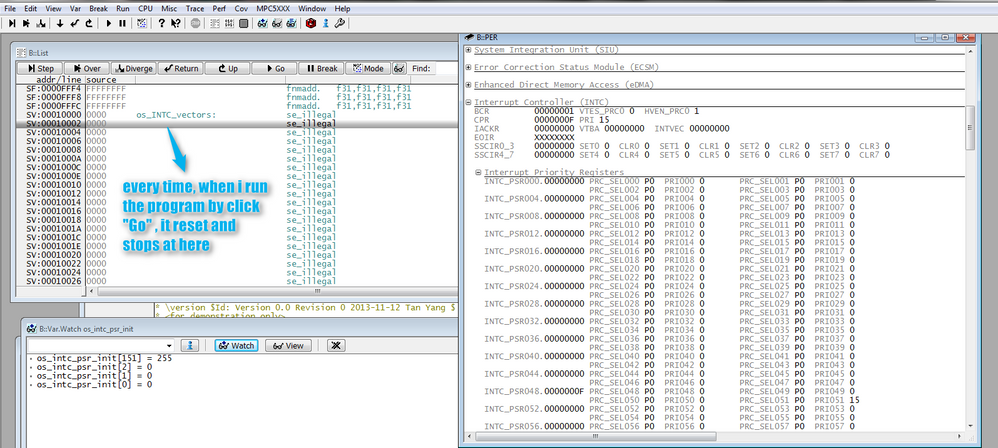

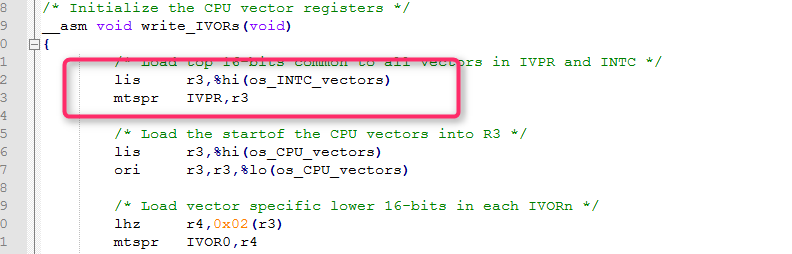

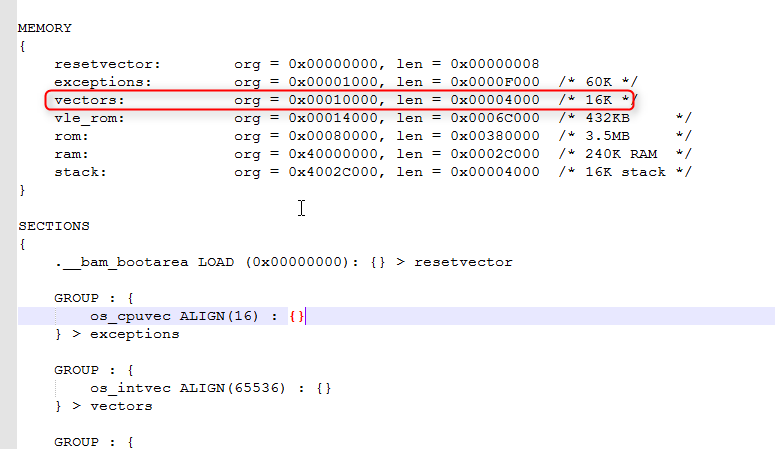

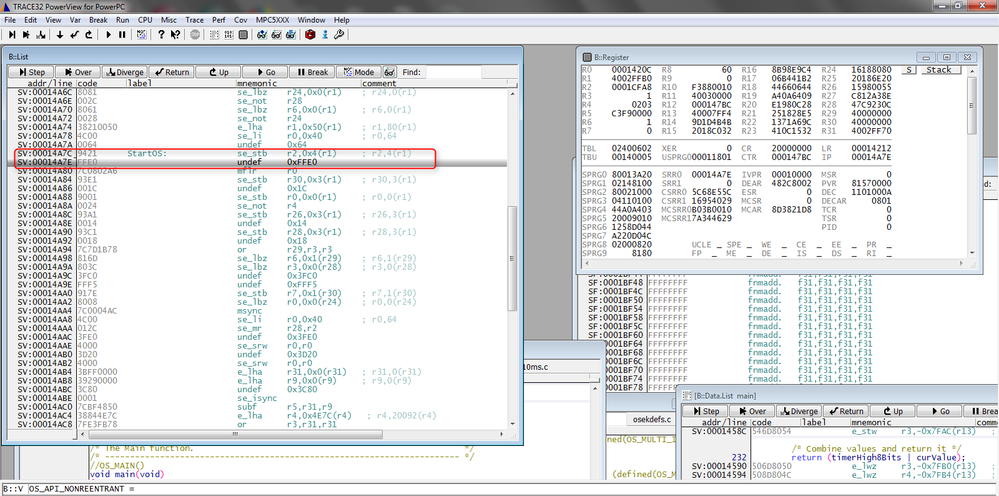

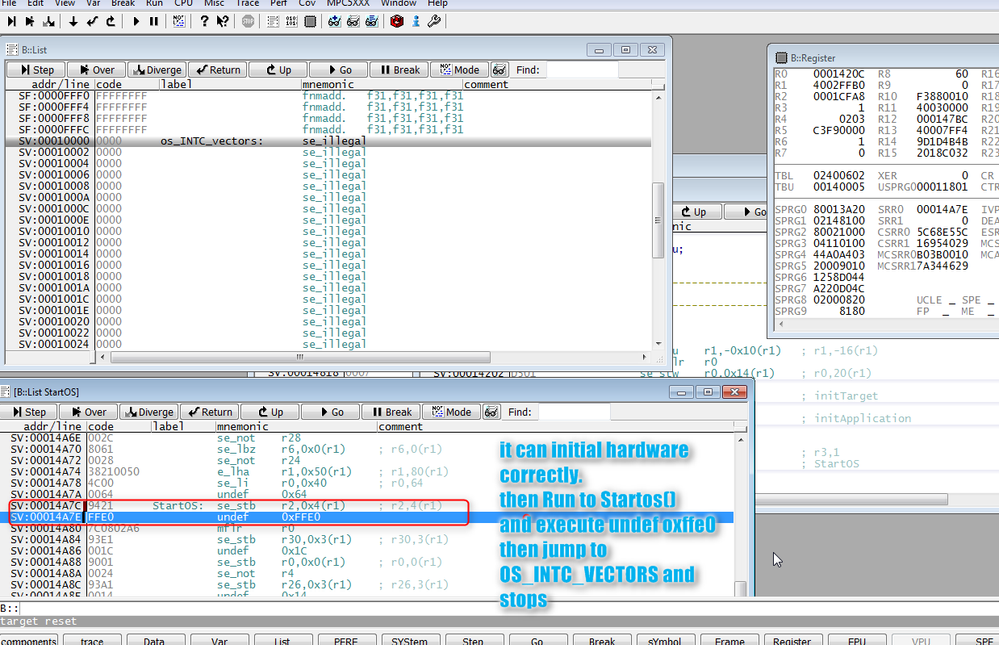

i have problem when debug the MPC5644A for EMIOS[0] use hardware interrupt mode. the os_INTC_vectors and os_CPU_vectors in osgen.s generated by RTA-OSEK, only enable emios[0], when debug with Trace32,

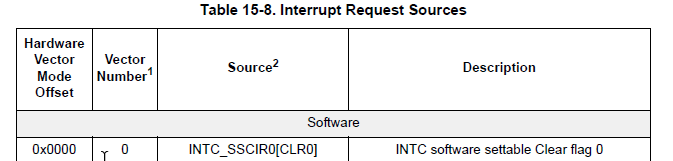

every time CPU reset at the entry of OS_INTC_vector table as below, from my understand, it should jump to 0X10330, which is Emios[0] interrupt entry point(0x10000+51x16). but it just jump to 0X10002.

i also attached the source code for my INTC config,

my question is:

(1) does the INTVEC register shows(0000) correct? what is the correct value for this application.

(2) could you give me some advise for this issue?

thanks for your help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Lukas,

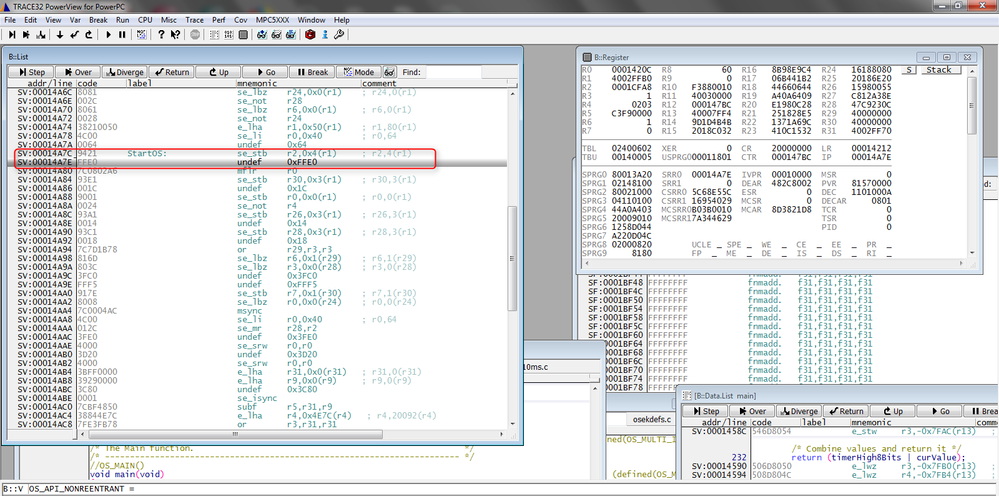

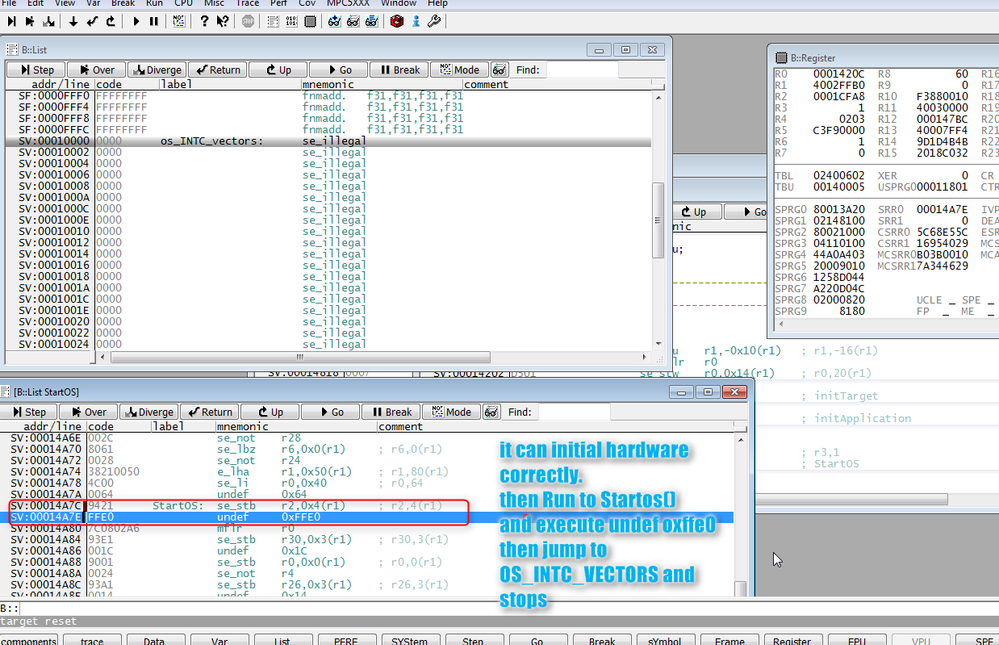

i still have problem to run the code. the problem is when the code run at undef 0xffe0, then it jump to interrupt vector0 and stops.

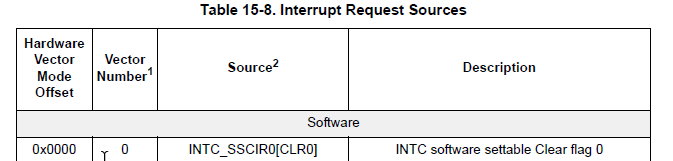

the first interrupt vector for MPC5644A is software intrrupt 0. at this time, the external interrupt is not enabled. i also have confidence for INTC right configure.

my question is: (1) what is the meaning of undef 0xffe0?

(2) from what or which register may helpful to find the root cause?

do you have any suggestion for this issue?

thanks for your reply!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

it seems you didn't initialized VTBA in IACKR register. The VTBA must be initialize to point to the beginning of interrupt vector table. Notice that it should be aligned to 0x800. So, if IVPR is set to 0x00010000 then this address is start address of IVOR exceptions and interrupt vector table should be at 0x00010800.

You can find SW example in:

https://www.nxp.com/docs/en/application-note/AN2865.pdf

https://www.nxp.com/webapp/sps/download/license.jsp?colCode=AN2865SW

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Lukas,

thanks for your reply, last week is Chinese new year holiday, i was on vacation. regarding your suggestion, i was little confused .

it seems you didn't initialized VTBA in IACKR register. The VTBA must be initialize to point to the beginning of interrupt vector table.

in hardware interrupt(vector) mode, do we need to initial the IACKR manually? or VTBA is automatically update from IVPR?

what i do in code is just initial the IVPR, from my understanding, the VTBA and the INTVEC is auto update no user touched in hardware interrupt mode.

Notice that it should be aligned to 0x800. So, if IVPR is set to 0x00010000 then this address is start address of IVOR exceptions and interrupt vector table should be at 0x00010800.

regarding the alignment, my setting is 65536 bytes align, so it should be also 0x800 aligned. and i do not understand why IVOR exceptions address have any related with interrupt vector table in hardware vector mode? Exception is located at OS_cpuvec area(0x1000).

thank you very much for your support!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm sorry, I completely mixed it up with e200z0 cores. It's a long time I used that.

In case of MPC5644A, IVPR is base address of interrupt vector table. Here it is necessary to initialize only IVPR.

For exceptions, it's necessary to initialize IVORn registers appropriately. The exceptions handlers must be placed somewhere after the interrupt vector table because the address is given by IVPR + IVORn. For example, interrupt vector table can be placed to 0x10000 (value in IVPR) and exception handlers to 0x12000 (that means IVORn registers will be initialized to 0x2---).

Sorry for confusion, hope it is more clear now.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Lukas,

i still have problem to run the code. the problem is when the code run at undef 0xffe0, then it jump to interrupt vector0 and stops.

the first interrupt vector for MPC5644A is software intrrupt 0. at this time, the external interrupt is not enabled. i also have confidence for INTC right configure.

my question is: (1) what is the meaning of undef 0xffe0?

(2) from what or which register may helpful to find the root cause?

do you have any suggestion for this issue?

thanks for your reply!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

thanks for your explanation, i can understand now.