- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX8MQ evk RMII MDIO read problem

IMX8MQ evk RMII MDIO read problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX8MQ evk RMII MDIO read problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

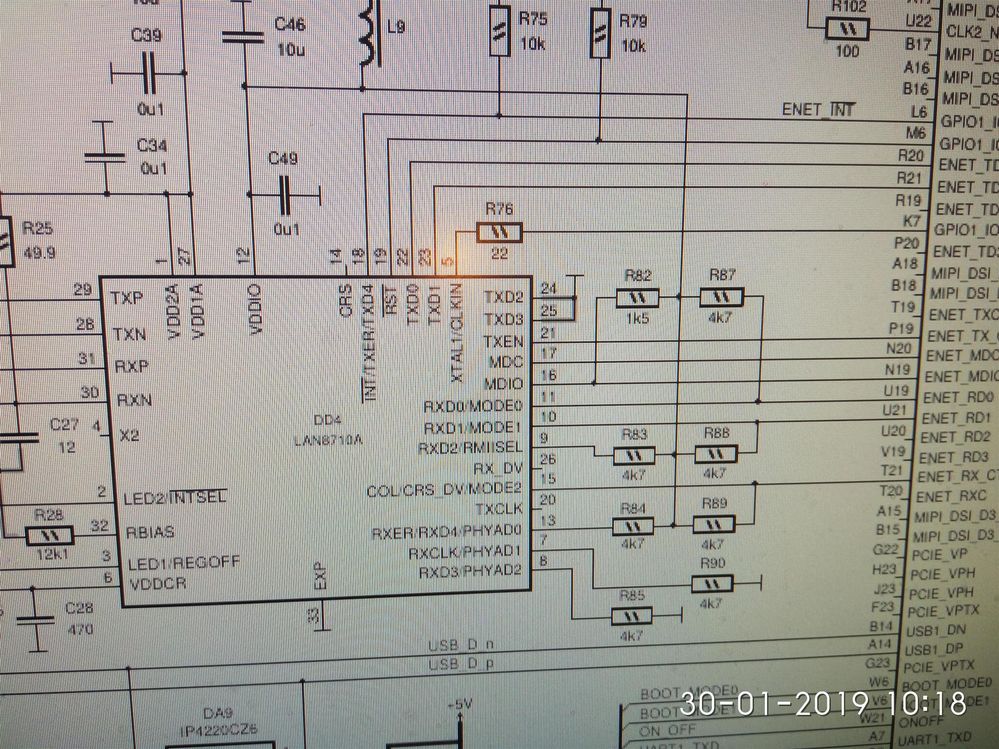

IMX8MQ evk u-boot problem with MDIO data read in RMII mode. I use LAN 8710a.

1) MDC -> ENET_MDC pad

2) MDIO -> ENET_MDIO pad

3) RMII clock -> GPIO1_IO00 - i use oscilloscope - i have 50MHz in this pin.

(Add code to set_clk_enet:

target = CLK_ROOT_ON | 0x01000000 |

CLK_ROOT_PRE_DIV(CLK_ROOT_PRE_DIV1) |

CLK_ROOT_POST_DIV(CLK_ROOT_POST_DIV1);

clock_set_target_val(ENET_PHY_REF_CLK_ROOT, target); ) - GPIO1_IO00

4)RMIISEL of LAN8710a pull up to VDD(mode RMII).

5) Settings

fsl-imx8mq-evk.dts

imx8mq-evk {

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MQ_IOMUXC_ENET_MDC_ENET1_MDC 0x3

MX8MQ_IOMUXC_ENET_MDIO_ENET1_MDIO 0x23

MX8MQ_IOMUXC_GPIO1_IO00_CCMSRCGPCMIX_ENET_PHY_REF_CLK_ROOT 0x59

MX8MQ_IOMUXC_ENET_TD3_ENET1_RGMII_TD3 0x56

MX8MQ_IOMUXC_ENET_TD2_ENET1_RGMII_TD2 0x56

MX8MQ_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x56

MX8MQ_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x56

MX8MQ_IOMUXC_ENET_RD3_ENET1_RGMII_RD3 0x56

MX8MQ_IOMUXC_ENET_RD2_ENET1_RGMII_RD2 0x56

MX8MQ_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x56

MX8MQ_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x56

MX8MQ_IOMUXC_ENET_TXC_ENET1_RGMII_TXC 0x56

MX8MQ_IOMUXC_ENET_RXC_ENET1_RGMII_RXC 0x56

MX8MQ_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x56

MX8MQ_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x56

MX8MQ_IOMUXC_GPIO1_IO09_GPIO1_IO9 0x19

>;

};

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

fsl,magic-packet;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

};

};

};

imx8mq_evk.h

/* ENET Config */

/* ENET1 */

#if defined(CONFIG_CMD_NET)

#define CONFIG_CMD_PING

#define CONFIG_CMD_DHCP

#define CONFIG_CMD_MII

#define CONFIG_MII

#define CONFIG_ETHPRIME "FEC"

#define CONFIG_FEC_MXC

#define FEC_QUIRK_ENET_MAC

#if 0

#define CONFIG_FEC_XCV_TYPE RGMII

#define CONFIG_FEC_MXC_PHYADDR 0

#define CONFIG_PHY_GIGE

#define CONFIG_PHY_ATHEROS

#else

#define CONFIG_FEC_XCV_TYPE RMII

#define CONFIG_PHY_SMSC

#define CONFIG_FEC_MXC_PHYADDR 1

#endif

#define IMX_FEC_BASE 0x30BE0000

#define CONFIG_PHYLIB

#endif

mii read 1 0

fec_mdio_read: phy: 01 reg:00 val:0x0

mii read 1 1

fec_mdio_read: phy: 01 reg:01 val:0x0

mii read 1 2

fec_mdio_read: phy: 01 reg:02 val:0x0

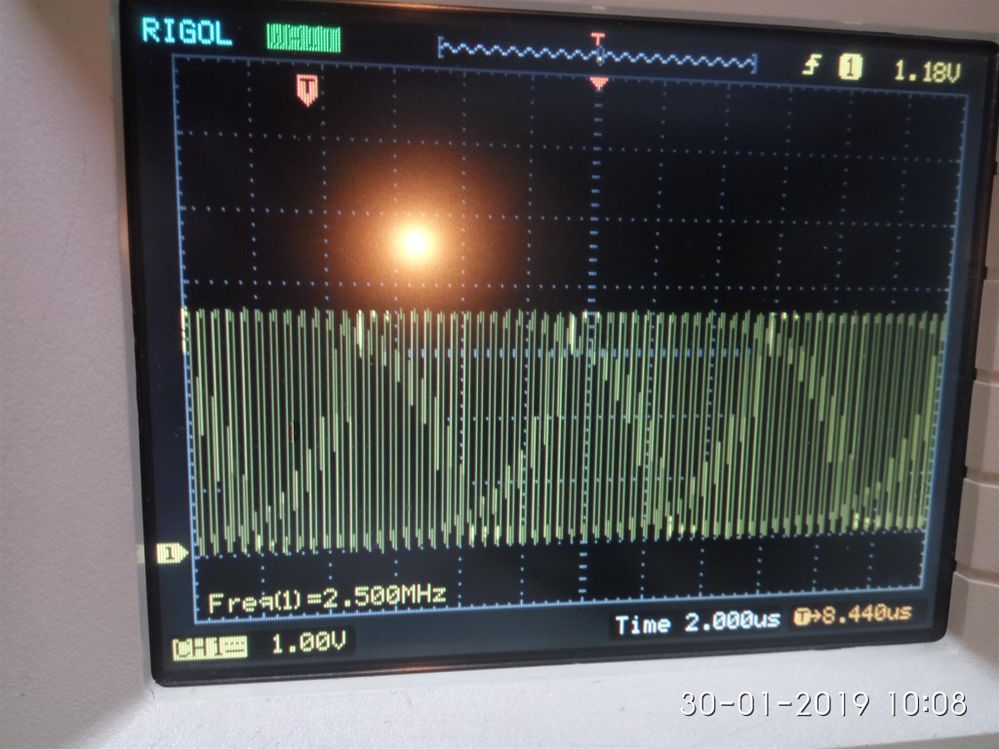

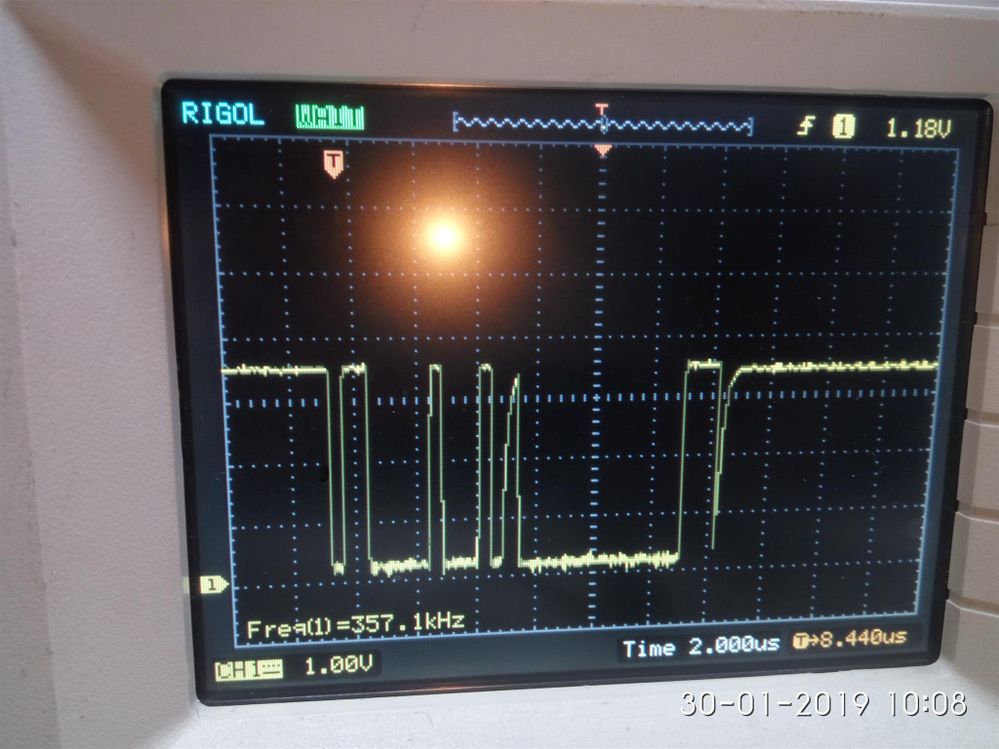

In oscilloscope:

ENET_MDC = 2,5 Mhz

When write - ENET_MDIO have correct signal, i saw this.

When read - ENET_MDIO read from phy correct data in oscilloscope - but in fec_mxc.c

val = (unsigned short)readl(ð->mii_data) - return always 0.

When write some values to LAN8710a phy registers, i read from phy registers that values (i saw this in oslillosope in ENET_MDIO pad), but mii_data always 0. FEC_IEVENT_MII event come.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vladimir

one can try latest official nxp uboot :

validation board (mx8mq-ddr3l-arm2.dts) uses rmii:

fsl-imx8mq-ddr3l-arm2.dts\freescale\dts\boot\arm64\arch - linux-imx - i.MX Linux kernel

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This not help. The only difference between mx8mq-ddr3l-arm2.dts and my .dts - i don't use MX8MQ_IOMUXC_ENET_TD2_ENET1_TX_CLK clock for RMII, i use MX8MQ_IOMUXC_GPIO1_IO00_CCMSRCGPCMIX_ENET_PHY_REF_CLK_ROOT. And phy interface num 1, not 3.

RMII clock -> GPIO1_IO00 - i use oscilloscope - i have 50MHz in this pin.

My scheme:

PIN MDC - 2,5 Mhz - all ok!

When send command mii read 1 2 - Read 2 register from 1 phy. LAN8710a send answer 0x7 by datasheet. PIN MDIO!

In this picture send command 01(ST) 10(OP-read) 0001(Phy address) 0010(Reg addr) 10 (TA -turn around) 000...111(DATA) answer from phy.

Question: How imx8m read value from MDIO pin?

By IMX8MDQLQRM.pdf:

command to MDIO set by write register ENET_MMFR - page 4354 (TA must be 10).

read from MDIO from this register also.

Why when i send command and have answer from phy (i saw this on osilloscope) - i have in register ENET_MMFR DATA = 000000? Read code static int fec_mdio_read(struct ethernet_regs *eth, uint8_t phyaddr,uint8_t regaddr)

writel(FEC_IEVENT_MII, ð->ievent);

reg = regaddr << FEC_MII_DATA_RA_SHIFT;

phy = phyaddr << FEC_MII_DATA_PA_SHIFT;

writel(FEC_MII_DATA_ST | FEC_MII_DATA_OP_RD | FEC_MII_DATA_TA |

phy | reg, ð->mii_data);

/* wait for the related interrupt */

start = get_timer(0);

while (!(readl(ð->ievent) & FEC_IEVENT_MII)) {

if (get_timer(start) > (CONFIG_SYS_HZ / 1000)) {

printf("Read MDIO failed...\n");

return -1;

}

}

/* clear mii interrupt bit */

writel(FEC_IEVENT_MII, ð->ievent);

/* it's now safe to read the PHY's register */

val = (unsigned short)readl(ð->mii_data);

printf("%s: phy: %02x reg:%02x val:%#x\n", __func__, phyaddr,regaddr, val);

by FEC_IEVENT_MII val always 0.

In datasheet - Turnaround time, programmed with ENETn_MMFR[TA]. Two bit-times are reserved for read

operations to switch the data bus from write to read. The PHY device presents its register contents

in the data phase and drives the bus from the second bit of the turnaround phase. How change time to switch the data bus from write to read? how long does it take - when TA set to 10 by datasheet?

How imx8m read value from MDIO pin and set this data to ENET_MMFR?