- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- No interrupt running Flexcomm in USART-mode with FIFO

No interrupt running Flexcomm in USART-mode with FIFO

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

No interrupt running Flexcomm in USART-mode with FIFO

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

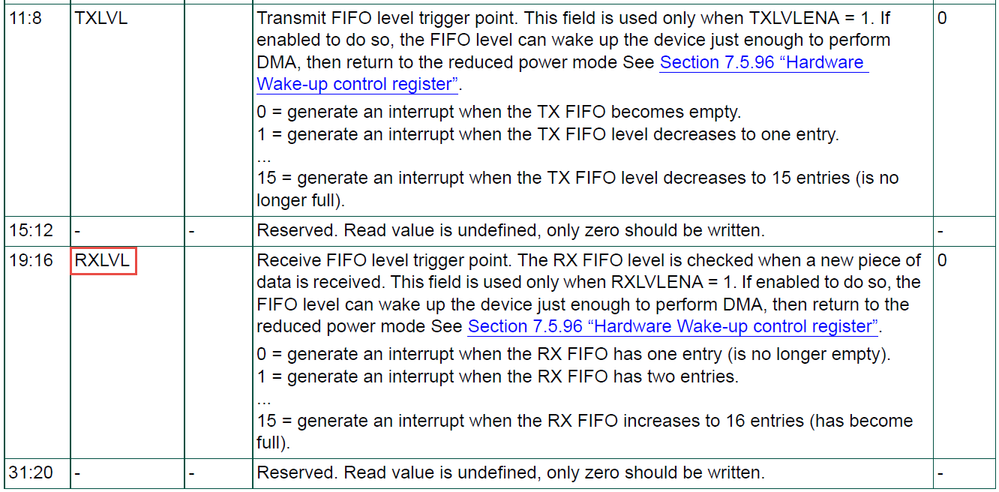

I have a problem finding information how to receive interrupt when the RX-FIFO in the Flexcomm module is partly filled. When the configured limit in the FIFO is reached, fine, but what if it is not reached. We have experience form the LPC24xx and LPC40xx peripherals where an interrupt is triggered as soon as the flow stopps and the remaining bytes in RX-FIFO can be read out. I have seen solutions with a separate timer but is this the only solution, really? I hope we miss something important!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, OK, sorry for being so unclear.

We have been using the LPC2468/LPC4078 for about 10 years (or more) and using a lot of UART peripherals in our application. We are looking at the LPC540xx or LPC546xx family that has the Flexcomm design for UART's. We are using FIFO to minimize number of interrupts. In the LPC24xx/LPC40xx uart peripheral there is a CTI (Character Time-out Indicator) that triggers an interrupt if no Rx activity has occurred in 3.5 to 4.5 character time so the fifo can be flushed to application level. So, for example, if the FIFO is configured to trigger an interrupt after 14 received characters and we only received 10 and no more (for a while), the CTI feature will handle this use-case.

How is this use-case handled in the Flexcomm peripheral design?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Niklas Swartz,

Thank you for clarification.

The CTI feature can provide a 'kind reminder' to read the remaining data in the receive FIFO, what a pity, the LPC54608 doesn't support this feature.

So I'd like to share a method to achieve the same function.

The LPC54608 can trigger an interrupt on FIFO receive level reached and the receive level is customized, it's available to receive all the in-coming data stream in the interrupt handler when setting an appropriate receive level.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Niklas Swartz,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

Actually, I was a bit confused with your question, I'll appreciate a lot if you can tell me which chip you use now.

Whether you want to implement the same application which is achieved in LPC24xx and LPC40xx in the chip.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------