- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- 5746C core

5746C core

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

5746C core

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

I'm currently using a MPC5746C, and i'm trying to startup the second core(z2), but without any success.

The SW application is really simple, as this is just for a demo project.

What I have done so far:

In the startup file for core0, I have the following code in the beginning:

; RCHW/ Boot header placement

.org base ; RCHW location ; base is set to 0x00FA0000

.long RCHW_VALUE ; This value is set to 0x005A0002

.long _start2 ; CPU2 entry point --> 0x00fa4020

.long 0

.long 0

.long _start ; CPU0 entry point

.long 0 ;

.long 0; Startup code

_start:/*A lot of RAM init code and so on...*

e_b main ; Jump to main

/*interrupt vectors allocated below*/

In main():

#define KEY_VALUE1 0x5AF0ul

#define KEY_VALUE2 0xA50Fuluint32_t mctl = MC_ME.MCTL.R;

/* enable core 2 in all modes */

MC_ME.CCTL3.R = 0x00FE;

/* Set Start address for core 2: Will reset and start */

MC_ME.CADDR3.R = (0x00fa4020 <<2) | 0x1;

MC_ME.MCTL.R = (mctl & 0xffff0000ul) | KEY_VALUE1;

MC_ME.MCTL.R = (mctl & 0xffff0000ul) | KEY_VALUE2; /* key value 2 always from MCTL */

while(1)

{

}

The main code is taken from a example in "S32 Design studio Power Architecture" I donwloaded from NXP.com

core2 startup code:

.globl _start2

; Startup code

.org 0x00fa4020

_start2:; Write 8000 dec to 0x40000500 in RAM

e_li r2,8000

e_li r3,0x4000

e_slwi r3,r3,16

e_add16i r3,r3,0x0500

se_stw r2,00(r3)

The main idea about this code:

I want to startup core2, and write a value(8000) to the memory address 0x40000500 ( This address is set to zero in core0's startup code).

The problem:

When I run this, it seems that core2 does not start up at all, as the address 0x40000500 still is zero after some time.

Or maybe core2 is starting up, but running somewhere else...

I have a breakpoint in core0's _start function, so I don't think that any resets is occurring. The core0s is running as expected, and ends up in my while(1) loop.

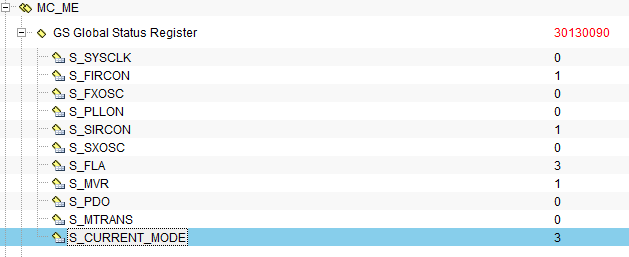

I can see the following in the debugger:

Current mode is DRUN

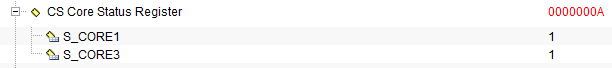

Both cores seems to be running according to the register:

The ADDR register is set as I expect:

Does someone have any idea what I have forgot?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I solved the issue during the weekend.

The problem was that the startup code for the second core where doing something strange, and made core2 crash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content