- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX7D Sabre power-down scheme

iMX7D Sabre power-down scheme

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX7D Sabre power-down scheme

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

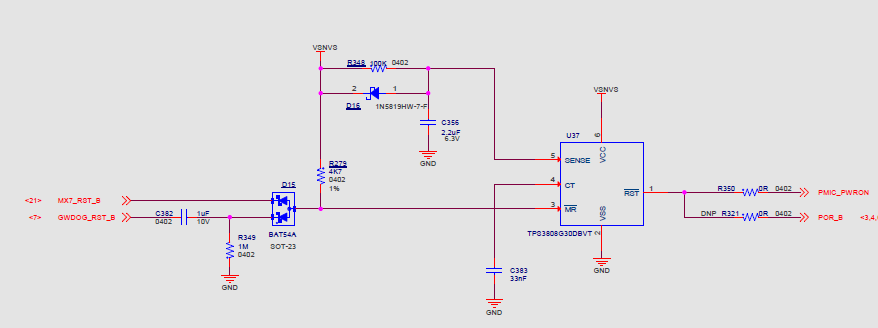

We have a CPU-board design based on the iMX7D Sabre evaluation board (MCIMX7D-SABRE). In recent light of some strange power-on / power-off behaviour with our board we have some questions about the purpose of U37 (TPS3808G30DBVT) in the Sabre Evaluation board. It would be very helpful for our debug effort if you could shed some light on how this specific part of the system is intended to work.

- Why does U37 both sense and is being supplied by the PMIC VSNVS output? How is this safe?

- Why is U37 set to have a threshold voltage of exactly 2.79V?

- Is U37 just a way of providing safe and reliable ORing of the watchdog signals (MX7_RST_B, GWDOG_RST_B etc.)?

During a power-down (with sufficient capacitance attached on the PSU_5V0 rail) we have seen the following:

- Power is removed and the voltage starts to drop slowly.

- When the voltage reaches 2.79V the PWRON signal from U37 is pulled low (as it should).

- The PMIC then transitions into its OFF state, thus consuming very little current.

- The low current consumption of the PMIC causes the input voltage to rise above 2.79V again due to the reduced load of the system.

- After approx 189ms (which is the the timeout set by C383), U37 asserts the PWRON signal again (as it should)

- This cycle continues for a while, causing the PWRON signal to look like a pulse-train.

Best regards,

Erlend

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

As I understand the following circuit is considered.

The mentioned circuit serves to meet general recommendation to remove power (voltage source)

for all components on the board in case of a processor reset. This avoids having to determine if a

component critical to rebooting the processor is in the necessary state to support a reboot.

So, total system POR may be recommended for reboot (via WDOG).

As for Your case, please check if VSNVS voltage is (always) provided.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------