- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- 关于imx6上的wm8962断电5分钟以上再重启系统,出现Speaker声音失真的问题

关于imx6上的wm8962断电5分钟以上再重启系统,出现Speaker声音失真的问题

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

关于imx6上的wm8962断电5分钟以上再重启系统,出现Speaker声音失真的问题

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

请问这个问题是否已解决?我有块板子也遇到相同问题。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

这个问题解决了吗,我也碰到了同样的问题。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

how many boards have this issue?

please check the signal integrity of MCLK.

is there a cap. connected in between clock and ground? what is the value?

if possible, could you send me the schematic of wm8962 part of your board?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

几乎每块板子都会有这个问题。

MCLK用示波器看了是24MHz,波形还算好,但是没有眼图测试仪器。

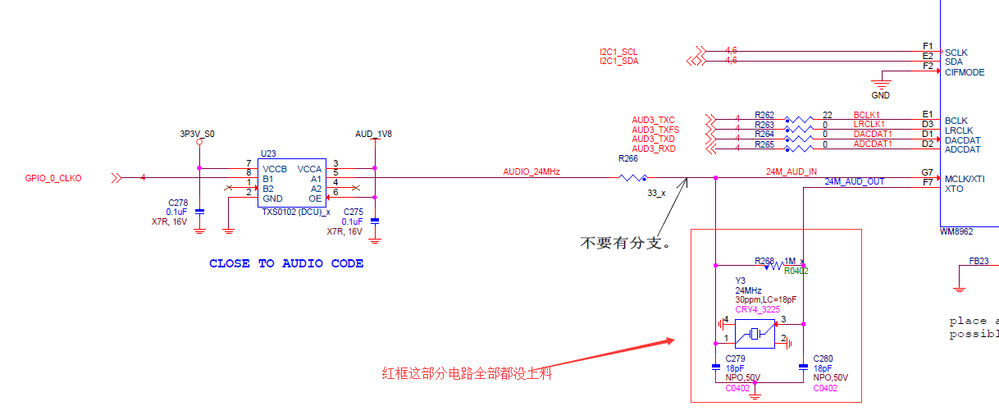

部分原理图如下:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hertz,

2 suggestions for your debugging the part.

(1) clock source code

In "linux/drivers/clk/imx/clk-imx6q.c "

/* * Let's initially set up CLKO with OSC24M, since

this configuration * is widely used by imx6q board designs to clock audio

codec. */

...

imx_clk_set_parent(clk[IMX6QDL_CLK_CKO2_SEL], clk[IMX6QDL_CLK_OSC]);

imx_clk_set_parent(clk[IMX6QDL_CLK_CKO], clk[IMX6QDL_CLK_CKO2]);

clk_set_rate(clk[IMX6QDL_CLK_CKO], 24000000); // add this line, please!

...

Then power on board, test audio.

(2) Remove R266 & Populate "Y3/R268/C279/C280" (断开 U23,把24MHz晶体焊上去)

Then power on board, test audio.

【Note】

I feel there are some issues with U23, so do above test, please!

Have a nice day.