- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso Config Tools

- :

- SDHC configuration in MCUXpresso config tools

SDHC configuration in MCUXpresso config tools

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SDHC configuration in MCUXpresso config tools

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think there might be a couple of issues with the MCUXpresso config tools around the SDHC in the K64 (my project uses the part MK64FN1M0VLQ12).

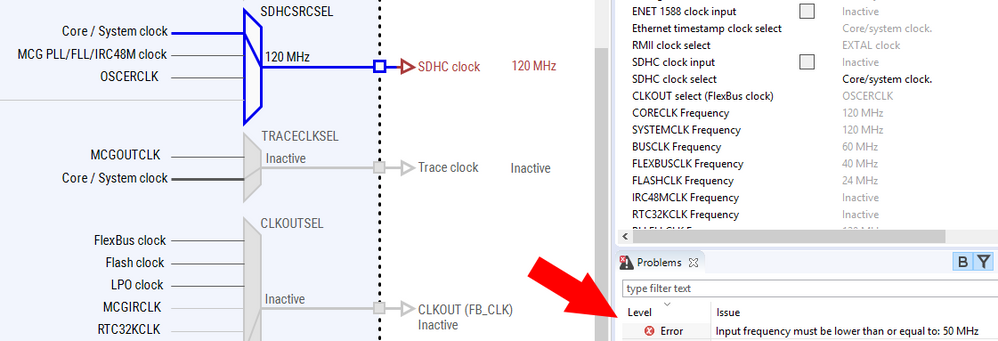

Firstly, the Clocks tool does not allow a SDHC source clock greater than 50MHz (SDHCSRCSEL), generating the error "Input frequency must be lower than or equal to: 50 MHz". The SDHC has a pre-scaler and divider that handle source clocks faster than 50MHz, and these are correctly configured by the SDK function SDHC_SetSdClock. Even the SDK example 'frdmk64f_fatfs_sdcard' uses the system/core clock at 120MHz as input to the SDHC.

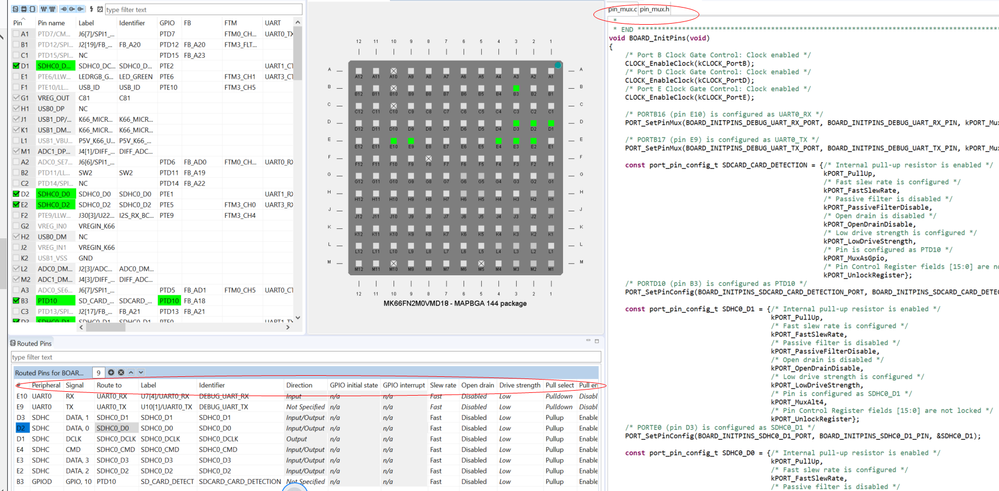

Secondly, the Pins tool does not completely configure the SDHC pins which need (at least) a fast slew rate to handle high signal frequencies, and possibly a high drive strength for some SD cards. Compare the code generated by the Pins tool for the SDHC pins:

/* PORTE0 (pin 1) is configured as SDHC0_D1 */

PORT_SetPinMux(PORTE, 0U, kPORT_MuxAlt4);

with the code used by the SDK example 'frdmk64f_fatfs_sdcard':

const port_pin_config_t porte0_pin1_config = {

kPORT_PullUp, /* Internal pull-up resistor is enabled */

kPORT_FastSlewRate, /* Fast slew rate is configured */

kPORT_PassiveFilterDisable, /* Passive filter is disabled */

kPORT_OpenDrainDisable, /* Open drain is disabled */

kPORT_HighDriveStrength, /* High drive strength is configured */

kPORT_MuxAlt4, /* Pin is configured as SDHC0_D1 */

kPORT_UnlockRegister /* Pin Control Register fields [15:0] are not locked */

};

PORT_SetPinConfig(PORTE, PIN0_IDX, &porte0_pin1_config); /* PORTE0 (pin 1) is configured as SDHC0_D1 */

This is the same for all SDHC pins.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Simon Haines ,

Thanks for interesting for MCUXrepsso Configuration tool.

For your first question about SDHC clock:

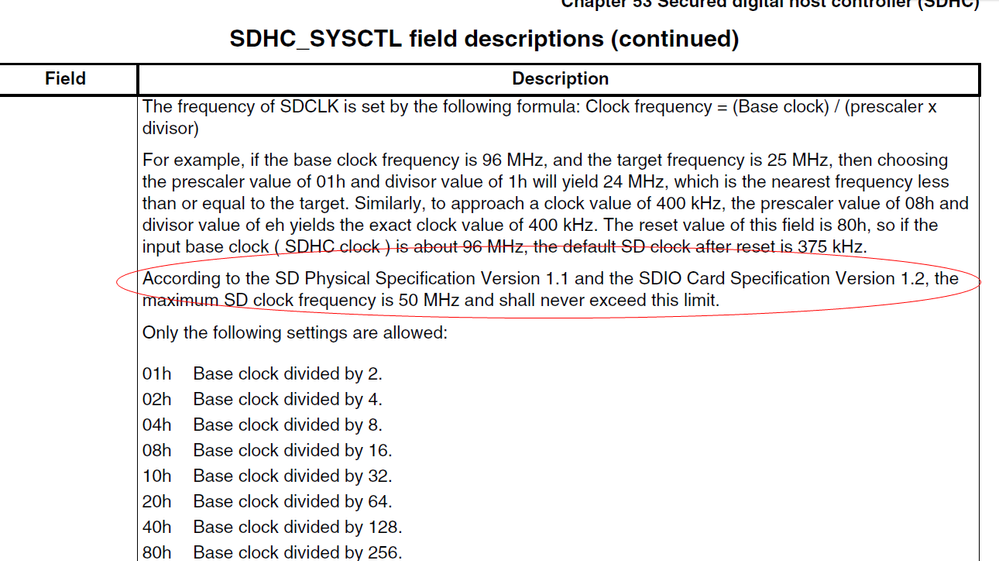

Please just pay attention that “According to the SD Physical Specification Version 1.1 and the SDIO Card Specification Version 1.2, the maximum SD clock frequency is 50 MHz and shall never exceed this limit.”

In SDCLK Frequency Select register part of MK64FN1M0 Reference Manual mentioned it .

About your second question , "the Pins tool does not completely configure the SDHC pins ", do you mind taking an example to tell me what does the configuration missing ?

You can configure the pins in "Routed Pins" view, then click "Update Project", will generate the code in pin_mux.c and pin_mux.h files :

Hope it helps,

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Alice,

Regarding my second question "the Pins tool does not completely configure the SDHC pins", I spent a lot of time debugging why some of my SD cards worked and some of them didn't until I compared my configuration to the SDK example that I noticed the SDK does extra pin configuration (see my first comment). I think routing pins to SDHC should at least also enable the pull-up resistor and high drive strength by default.

Regarding my first question, it is perfectly OK to set SIM_SOPT2:SDHCSRC to a clock greater than 50MHz, as long as you set SDHC_SYSCTL:SDCLKFS and SDHC_SYSCTL:DVS to appropriate values. The MK64FN1M0 Reference Manual says:

For example, if the base clock frequency is 96 MHz, and the target frequency is 25 MHz, then choosing the prescaler value of 01h and divisor value of 1h will yield 24 MHz, which is the nearest frequency less than or equal to the target.

The problem is that the MCUXpresso Clocks tool does not allow you to set the base clock of the SDHC peripheral if it is over 50MHz. This is a bug. The Clocks tool should allow a base clock greater than 50MHz, and use the SDK function SDHC_SetSdClock(SDHC_Type *base, uint32_t srcClock_Hz, uint32_t busClock_Hz) to set the correct prescaler and divider.

Hope this helps,

Simon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Simon,

Yes, only refer to the register data , can set clock greater than 50MHZ, while there are some specification we

need to follow :

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------