- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- enhanced boot mcuexpresso

enhanced boot mcuexpresso

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is there any MCU_Expresso compatible assembly to do the following for the LPCXpresso54608?

3.3.2.6 Modifications to startup code to enable enhanced boot support

Several modifications need to be made to the startup code to enable enhanced boot

support. The value at offset 0x24 in the image must contain an enhanced image marker

and the value at offset 0x28 must point to a valid image header in the image. See the box

below for an example setup using a Single Enhanced image. Changes are in bold and

made to the vector table are of the startup code.

; Vector Table Mapped to Address 0 at Reset

AREA RESET, DATA, READONLY

EXPORT __Vectors

__Vectors DCD __initial_sp ; Top of Stack

DCD Reset_Handler ; Reset Handler

DCD NMI_Handler

DCD HardFault_Handler

DCD MemManage_Handler

DCD BusFault_Handler

DCD UsageFault_Handler

__vector_table_0x1c

DCD 0 ; Checksum of the first 7 words

DCD 0

DCD 0xEDDC9494 ; Enhanced image marker, set to 0x0 for legacy boot

IMPORT imageHeader

UM10912 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 2.1 — 9 November 2017 30 of 1174

NXP Semiconductors UM10912

Chapter 3: LPC546xx Boot process

DCD imageHeader ; Pointer to enhanced image header, use 0x0 for legacy

boot

The image header for the startup code must be located somewhere in non-volatile

memory. A simple image header that doesn’t perform CRC is shown below. All field sizes

are 32-bits.

/* Image header */

const IMAGEHEADER_T imageHeader = {

IMAGE_ENH_BLOCK_MARKER, /* Required marker for image header */

IMG_NO_CRC, /* No CRC, makes development easier */

0x00000000, /* crc32_len */

0x00000000, /* crc32_val */

0x00000000 /* version */

};

I cannot get the IDE/assembler to recognize any of the arm instructions.

Thanks!

Ben

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I resolved my issue.

I had section variables that were overwriting first 7 words starting at FLASH address 0x0.

Used Vector table in .C to enable single enhanced image:

__attribute__ ((used, section(".isr_vector")))

void (* const g_pfnVectors_Boot[])(void) = {

// Core Level - CM4

&_vStackTop, // The initial stack pointer

ResetISR, // The reset handler

NMI_Handler, // The NMI handler

HardFault_Handler, // The hard fault handler

MemManage_Handler, // The MPU fault handler

BusFault_Handler, // The bus fault handler

UsageFault_Handler, // The usage fault handler

__valid_user_code_checksum, // LPC MCU checksum

0, // ECRP

SINGLE_ENHANCED_IMAGE_SIGNATURE, // Reserved

(void *) &image_header, // Reserved

SVC_Handler, // SVCall handler

DebugMon_Handler, // Debug monitor handler

0, // Reserved

PendSV_Handler, // The PendSV handler

SysTick_Handler, // The SysTick handler

// Chip Level - LPC54608

WDT_BOD_IRQHandler, // 16: Windowed watchdog timer, Brownout detect

DMA0_IRQHandler, // 17: DMA controller

GINT0_IRQHandler, // 18: GPIO group 0

GINT1_IRQHandler, // 19: GPIO group 1

PIN_INT0_IRQHandler, // 20: Pin interrupt 0 or pattern match engine slice 0

PIN_INT1_IRQHandler, // 21: Pin interrupt 1or pattern match engine slice 1

PIN_INT2_IRQHandler, // 22: Pin interrupt 2 or pattern match engine slice 2

PIN_INT3_IRQHandler, // 23: Pin interrupt 3 or pattern match engine slice 3

UTICK0_IRQHandler, // 24: Micro-tick Timer

MRT0_IRQHandler, // 25: Multi-rate timer

CTIMER0_IRQHandler, // 26: Standard counter/timer CTIMER0

CTIMER1_IRQHandler, // 27: Standard counter/timer CTIMER1

SCT0_IRQHandler, // 28: SCTimer/PWM

CTIMER3_IRQHandler, // 29: Standard counter/timer CTIMER3

FLEXCOMM0_IRQHandler, // 30: Flexcomm Interface 0 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM1_IRQHandler, // 31: Flexcomm Interface 1 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM2_IRQHandler, // 32: Flexcomm Interface 2 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM3_IRQHandler, // 33: Flexcomm Interface 3 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM4_IRQHandler, // 34: Flexcomm Interface 4 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM5_IRQHandler, // 35: Flexcomm Interface 5 (USART, SPI, I2C,, FLEXCOMM)

FLEXCOMM6_IRQHandler, // 36: Flexcomm Interface 6 (USART, SPI, I2C, I2S,, FLEXCOMM)

FLEXCOMM7_IRQHandler, // 37: Flexcomm Interface 7 (USART, SPI, I2C, I2S,, FLEXCOMM)

ADC0_SEQA_IRQHandler, // 38: ADC0 sequence A completion.

ADC0_SEQB_IRQHandler, // 39: ADC0 sequence B completion.

ADC0_THCMP_IRQHandler, // 40: ADC0 threshold compare and error.

DMIC0_IRQHandler, // 41: Digital microphone and DMIC subsystem

HWVAD0_IRQHandler, // 42: Hardware Voice Activity Detector

USB0_NEEDCLK_IRQHandler, // 43: USB Activity Wake-up Interrupt

USB0_IRQHandler, // 44: USB device

RTC_IRQHandler, // 45: RTC alarm and wake-up interrupts

Reserved46_IRQHandler, // 46: Reserved interrupt

Reserved47_IRQHandler, // 47: Reserved interrupt

PIN_INT4_IRQHandler, // 48: Pin interrupt 4 or pattern match engine slice 4 int

PIN_INT5_IRQHandler, // 49: Pin interrupt 5 or pattern match engine slice 5 int

PIN_INT6_IRQHandler, // 50: Pin interrupt 6 or pattern match engine slice 6 int

PIN_INT7_IRQHandler, // 51: Pin interrupt 7 or pattern match engine slice 7 int

CTIMER2_IRQHandler, // 52: Standard counter/timer CTIMER2

CTIMER4_IRQHandler, // 53: Standard counter/timer CTIMER4

RIT_IRQHandler, // 54: Repetitive Interrupt Timer

SPIFI0_IRQHandler, // 55: SPI flash interface

FLEXCOMM8_IRQHandler, // 56: Flexcomm Interface 8 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM9_IRQHandler, // 57: Flexcomm Interface 9 (USART, SPI, I2C, FLEXCOMM)

SDIO_IRQHandler, // 58: SD/MMC

CAN0_IRQ0_IRQHandler, // 59: CAN0 interrupt0

CAN0_IRQ1_IRQHandler, // 60: CAN0 interrupt1

CAN1_IRQ0_IRQHandler, // 61: CAN1 interrupt0

CAN1_IRQ1_IRQHandler, // 62: CAN1 interrupt1

USB1_IRQHandler, // 63: USB1 interrupt

USB1_NEEDCLK_IRQHandler, // 64: USB1 activity

ETHERNET_IRQHandler, // 65: Ethernet

ETHERNET_PMT_IRQHandler, // 66: Ethernet power management interrupt

ETHERNET_MACLP_IRQHandler, // 67: Ethernet MAC interrupt

EEPROM_IRQHandler, // 68: EEPROM interrupt

LCD_IRQHandler, // 69: LCD interrupt

SHA_IRQHandler, // 70: SHA interrupt

SMARTCARD0_IRQHandler, // 71: Smart card 0 interrupt

SMARTCARD1_IRQHandler, // 72: Smart card 1 interrupt

}; /* End of g_pfnVectors */

... Poor understanding on my part.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check the LPC1700 secondary USB bootloader as reference:

http://cache.nxp.com/docs/en/application-note/AN10866.zip

I hope this helps,

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

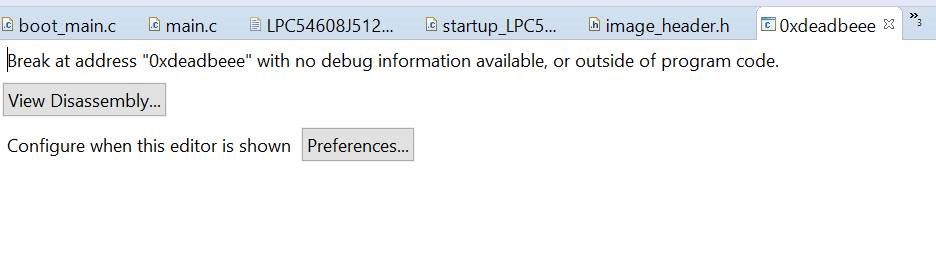

I have gotten past one of my hurdles. I have a section placement variable to write the single enhanced image enable to 0x24 in FLASH. At 0x28 I have the pointer to the image header which I stored in .rodata.

The ROM bootloader successfully jumps to my single enhanced image (this will be my secondary bootloader). My secondary bootloader consumes FLASH space 0x0 to 0x7FFF. I created a dummy app that blinks LEDS, it consumes FLASH space 0x8000 to 0x7FFFF. My secondary bootloader, at this moment, simply jumps to my dummy app.

When I flash the dummy app, then flash the secondary bootlaoder all works well (I see blinking LEDS).

However, when I reset I end up in some invalid memory space:

Any thoughts would be greatly appreciated!

PS, I have loaded additional symbol files in the bootloader so I can debug both bootloader and application, so this is likely not a debug issue.

Thanks!

Ben

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I resolved my issue.

I had section variables that were overwriting first 7 words starting at FLASH address 0x0.

Used Vector table in .C to enable single enhanced image:

__attribute__ ((used, section(".isr_vector")))

void (* const g_pfnVectors_Boot[])(void) = {

// Core Level - CM4

&_vStackTop, // The initial stack pointer

ResetISR, // The reset handler

NMI_Handler, // The NMI handler

HardFault_Handler, // The hard fault handler

MemManage_Handler, // The MPU fault handler

BusFault_Handler, // The bus fault handler

UsageFault_Handler, // The usage fault handler

__valid_user_code_checksum, // LPC MCU checksum

0, // ECRP

SINGLE_ENHANCED_IMAGE_SIGNATURE, // Reserved

(void *) &image_header, // Reserved

SVC_Handler, // SVCall handler

DebugMon_Handler, // Debug monitor handler

0, // Reserved

PendSV_Handler, // The PendSV handler

SysTick_Handler, // The SysTick handler

// Chip Level - LPC54608

WDT_BOD_IRQHandler, // 16: Windowed watchdog timer, Brownout detect

DMA0_IRQHandler, // 17: DMA controller

GINT0_IRQHandler, // 18: GPIO group 0

GINT1_IRQHandler, // 19: GPIO group 1

PIN_INT0_IRQHandler, // 20: Pin interrupt 0 or pattern match engine slice 0

PIN_INT1_IRQHandler, // 21: Pin interrupt 1or pattern match engine slice 1

PIN_INT2_IRQHandler, // 22: Pin interrupt 2 or pattern match engine slice 2

PIN_INT3_IRQHandler, // 23: Pin interrupt 3 or pattern match engine slice 3

UTICK0_IRQHandler, // 24: Micro-tick Timer

MRT0_IRQHandler, // 25: Multi-rate timer

CTIMER0_IRQHandler, // 26: Standard counter/timer CTIMER0

CTIMER1_IRQHandler, // 27: Standard counter/timer CTIMER1

SCT0_IRQHandler, // 28: SCTimer/PWM

CTIMER3_IRQHandler, // 29: Standard counter/timer CTIMER3

FLEXCOMM0_IRQHandler, // 30: Flexcomm Interface 0 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM1_IRQHandler, // 31: Flexcomm Interface 1 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM2_IRQHandler, // 32: Flexcomm Interface 2 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM3_IRQHandler, // 33: Flexcomm Interface 3 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM4_IRQHandler, // 34: Flexcomm Interface 4 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM5_IRQHandler, // 35: Flexcomm Interface 5 (USART, SPI, I2C,, FLEXCOMM)

FLEXCOMM6_IRQHandler, // 36: Flexcomm Interface 6 (USART, SPI, I2C, I2S,, FLEXCOMM)

FLEXCOMM7_IRQHandler, // 37: Flexcomm Interface 7 (USART, SPI, I2C, I2S,, FLEXCOMM)

ADC0_SEQA_IRQHandler, // 38: ADC0 sequence A completion.

ADC0_SEQB_IRQHandler, // 39: ADC0 sequence B completion.

ADC0_THCMP_IRQHandler, // 40: ADC0 threshold compare and error.

DMIC0_IRQHandler, // 41: Digital microphone and DMIC subsystem

HWVAD0_IRQHandler, // 42: Hardware Voice Activity Detector

USB0_NEEDCLK_IRQHandler, // 43: USB Activity Wake-up Interrupt

USB0_IRQHandler, // 44: USB device

RTC_IRQHandler, // 45: RTC alarm and wake-up interrupts

Reserved46_IRQHandler, // 46: Reserved interrupt

Reserved47_IRQHandler, // 47: Reserved interrupt

PIN_INT4_IRQHandler, // 48: Pin interrupt 4 or pattern match engine slice 4 int

PIN_INT5_IRQHandler, // 49: Pin interrupt 5 or pattern match engine slice 5 int

PIN_INT6_IRQHandler, // 50: Pin interrupt 6 or pattern match engine slice 6 int

PIN_INT7_IRQHandler, // 51: Pin interrupt 7 or pattern match engine slice 7 int

CTIMER2_IRQHandler, // 52: Standard counter/timer CTIMER2

CTIMER4_IRQHandler, // 53: Standard counter/timer CTIMER4

RIT_IRQHandler, // 54: Repetitive Interrupt Timer

SPIFI0_IRQHandler, // 55: SPI flash interface

FLEXCOMM8_IRQHandler, // 56: Flexcomm Interface 8 (USART, SPI, I2C, FLEXCOMM)

FLEXCOMM9_IRQHandler, // 57: Flexcomm Interface 9 (USART, SPI, I2C, FLEXCOMM)

SDIO_IRQHandler, // 58: SD/MMC

CAN0_IRQ0_IRQHandler, // 59: CAN0 interrupt0

CAN0_IRQ1_IRQHandler, // 60: CAN0 interrupt1

CAN1_IRQ0_IRQHandler, // 61: CAN1 interrupt0

CAN1_IRQ1_IRQHandler, // 62: CAN1 interrupt1

USB1_IRQHandler, // 63: USB1 interrupt

USB1_NEEDCLK_IRQHandler, // 64: USB1 activity

ETHERNET_IRQHandler, // 65: Ethernet

ETHERNET_PMT_IRQHandler, // 66: Ethernet power management interrupt

ETHERNET_MACLP_IRQHandler, // 67: Ethernet MAC interrupt

EEPROM_IRQHandler, // 68: EEPROM interrupt

LCD_IRQHandler, // 69: LCD interrupt

SHA_IRQHandler, // 70: SHA interrupt

SMARTCARD0_IRQHandler, // 71: Smart card 0 interrupt

SMARTCARD1_IRQHandler, // 72: Smart card 1 interrupt

}; /* End of g_pfnVectors */

... Poor understanding on my part.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What errors are you getting? Perhaps post the code you are trying to assemble?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After further digging it's due to the toolchain used by MCUXpresso. I either need the assembly for ARM-GCC to accomplish this, or the equivalent code in C.

I will try to port in the meantime.

Thanks!

Ben