- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- UJA1169TK/X SBC wakeup by CAN and WAKE pin

UJA1169TK/X SBC wakeup by CAN and WAKE pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

UJA1169TK/X SBC wakeup by CAN and WAKE pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We have requirement, SBC is requested to have wake up via CAN and switch change of state on wake up pin.

The SW shall configure the following registers as below:

- CWE bit from Transceiver event capture enable register (23h) shall be set to logic 1; (this will enable the CAN wake up mechanism)

- WPRE bit from WAKE pin event enable register (4Ch) shall be set to logic 1; (this will enable rising edge detection on WAKE pin)

- WPFE bit from WAKE pin event enable register (4Ch) shall be set to logic 0; (this will disable falling edge detection on WAKE pin).

We observed that wake up by pin happens successfully, and we have a query on CAN standard wake-up

- What is wake-up pattern, how we can send and how to test?

Please let us know how to send wake-up pattern and how to test wake by CAN

We are waiting for your response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Siva,

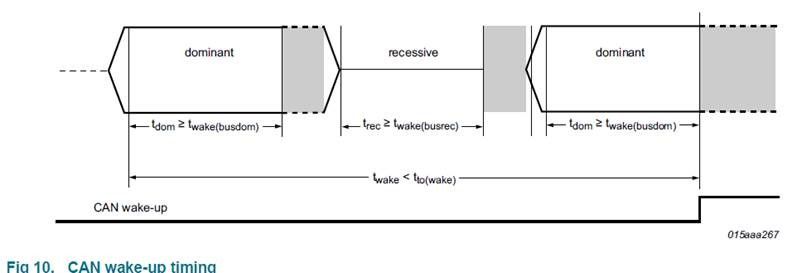

In the datasheet, page 26, you can see the figure as below.

SBC needs to receive dominant->recessive->dominant sequence longer period than twake(busdom) and twake(busrec).within less than to(wake).

This should be more or less same for all CAN transceivers to wake-up by CAN wake-up pattern.

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tomas,

Thanks for your quick response,

we are facing a problem while putting SBC in to sleep mode.

We observed that SBC receives a Sleep mode command (MC = 001), it immediately switches to Reset mode. and

- Global event status register (address 60h) : SYSE (system event pending at address 0x61) bit is set,

- We are trying to clear System event status register (address 61h): power-on (PO ) and watchdog failure (WDF) by writing 1 to corresponding bits but it is not clearing.

For reference find our observations below:

- Read Command: 0xC100, Respose from SBC 0xC101

Read Command: 0xC300, Respose from SBC 0xC311

Read Command: 0xC500, Respose from SBC 0xC500

- Read Command: 0xC700, Respose from SBC 0xC700

- Read Command: 0xC900, Respose from SBC 0xC900

Let us to know any thing else need to configure other than these registers:

- We cleared the FNMC by programing non-volatile memory (NVM) registers (Software Development mode disabled).

- SBC watchdog control register (0x00h) in WMC : Timeout, NWP: 128ms

- Enabled the Transceiver event capture enable register (Write command: 0x4601)

- Enabled WAKE pin event capture enable register (Write command: 0x9802)

- Enabled CAN control register (Write command: 0x4001)

- Enabled Mode control register (Write command: 0x0207) to enter in to Normal mode

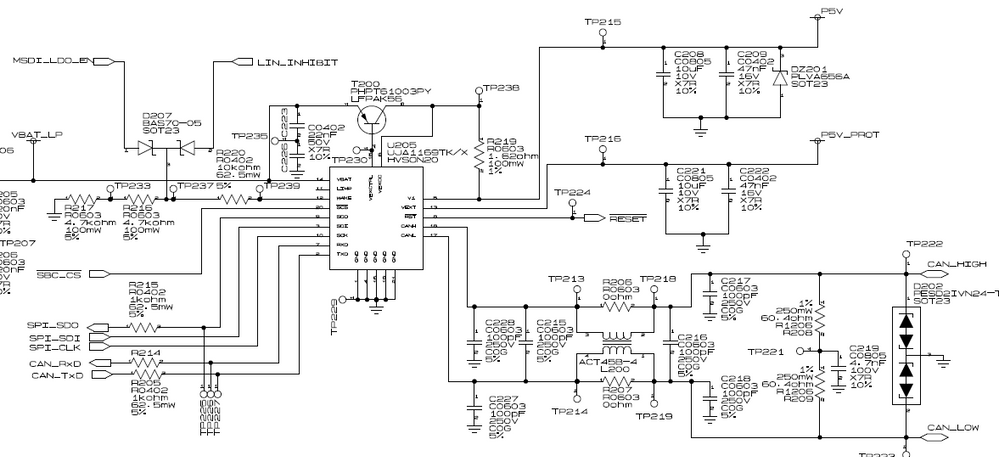

- Below is the schematic we have

Please help us to configure SBC in to sleep mode.

We are waiting for your response.

Regards,

Siva Sankar Chandika

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Siva,

Enter to Sleep means V1 is OFF, then.

So, microcontroller may not have power any more.

If RSTN of microcontroller was connected to RSTN of UJA1169, microcontroller can set the pin low and UJA1169 is reset.

This can often happen in PCB design, but, this can only be solved by disconnecting RSTN of UJA1169 from RSTN of controller.

Best regards,

Tomas