- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- MK10 ADC input sampling waveform

MK10 ADC input sampling waveform

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MK10 ADC input sampling waveform

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi team,

We are using MK10DN512VLQ10 in our system. During ADC testing, I found that ADC error will change according to external input voltage. So I removed all external capacitors and applied a standard voltage source to the input circuit ,

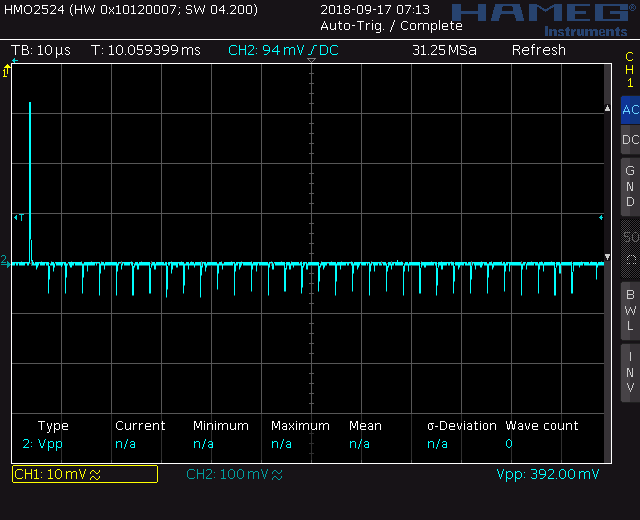

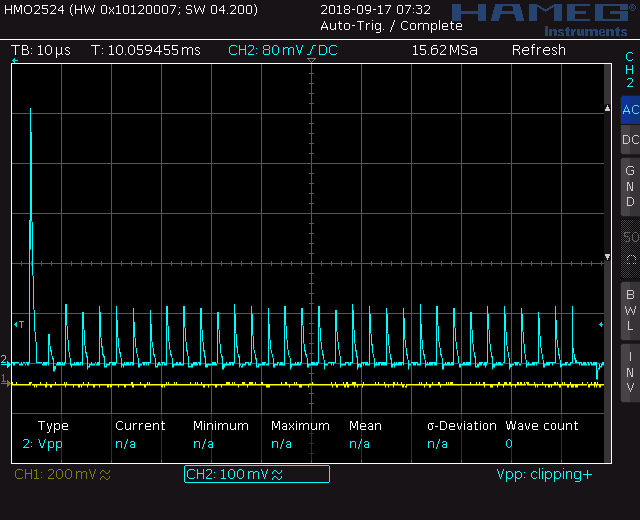

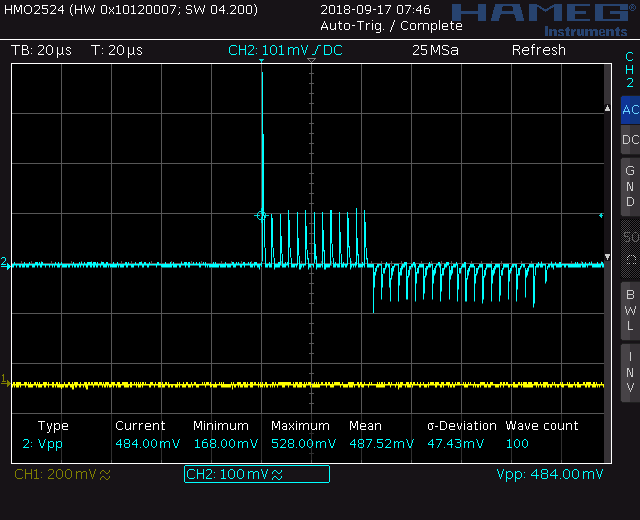

then I measured the voltage on the pin and saved the screenshots as below(probe was AC coupled with short spring type ground):

I thought a typical ADC sampling waveform should only contain negative spike(due to charging of internal sampling capacitor), but I also captured some positive spike and sometimes even change from positive to negative(the last screenshot above). I also didn't expect the first unusual high level spike.

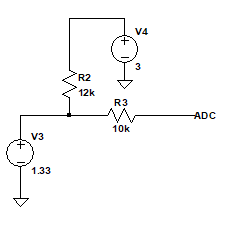

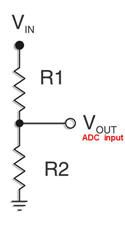

The modified external circuit just like below:

Below is the test setup, this is a NTC sensor circuit with capacitor removed and NTC disconnected. The voltage is given by a voltage generator, I also checked the output of the voltage generator, no spike was found.

Are those behavior caused by the internal design of the MCU?

Please help!

Thanks and regards!

Wei Xu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wei Xu,

(probe was AC coupled with short spring type ground)

Have you try to use other type of probe?

Or other voltage signal, something like resistor divider:

A typical ADC sampling waveform should only contain negative spike(As described in AN4373 Cookbook for SAR ADC measurements), I have never noticed there will be positive spike.

Would you please edit this thread and attached the test project, so that I can test it on TWR-K60D100M board.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin,

Thanks for your reply!

I updated the thread yesterday but then I found that I couldn't see your reply anymore, so I reply to you today.

I also tried another probe, it is the same result.

Our origin test setup is a resistor devider, but I found out that at some voltage the error is larger. So I disconnected the resistor and tried a voltage calibrator, and then I found out during I increase the input voltage by 10mV step, the error of ADC will reach a peak ever 100mV, then decrease then after increased another 100mV reach another error peak.

I also read the AN4373 guide, it mentioned below details in page 4:

In a case of redistribution charging architecture of SAR ADC or if a presampling circuit is used, then the initial voltage can be equal to VREFL or VREFH. In some special cases, this value can be set to (VREFH - VREFL)/2 in order to ensure lower voltage stress of capacitor. Usually when sequential sampling is used, then the initial voltage VCSH0 is equal to the previous channel voltage conversion.

Does this means it is the internal presampling circuit that caused this behaviour? Maybe the internal circuit detect the input voltage first(using comparator etc,.) and then judge which nearst voltage level the sampling capacitor should be charged to?

Thanks and regards!

Wei Xu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will check it with AE team. If you can attached your test project, that would be better.