- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx6sx custom DP83867 ethernet PHY not working

imx6sx custom DP83867 ethernet PHY not working

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx6sx custom DP83867 ethernet PHY not working

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

We have an imx6sx in a custom board with 2 ethernet phys: one is a TI DP83867 and one is an NXP TJA1100 automotive phy. The design is based on the Sabresd dev board. I have a problem configuring the mdio bus to recongnize both phys. The TJA1101 is always seen on the bus but the DP isn't. The TJA1101 uses RMII mode and the DP uses RGMII mode. The phy side of the dp is fine; clocks to the DP are fine - 25MHZ because it's limited to 100Mbits; the DP driver is in the kernel; the activity led bursts into life both ends when a cable is connected; the DP is recognized in u-boot as eth0 [ PRIME ] ( I had to change the mask in fec_phy_init function in fec_mxc.c, because the phy id is 0x1f ). However, linux cannot find the phy and doesn't load the driver ! The mdio bus cannot see the DP phy but can see the TJA1101.

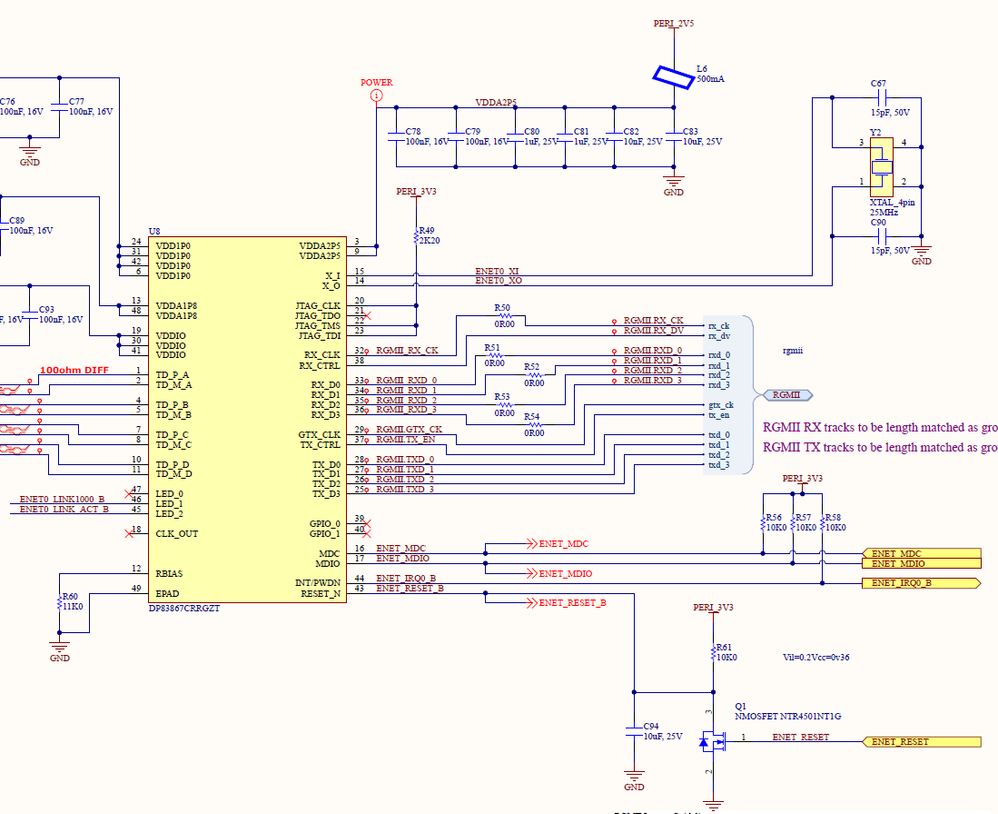

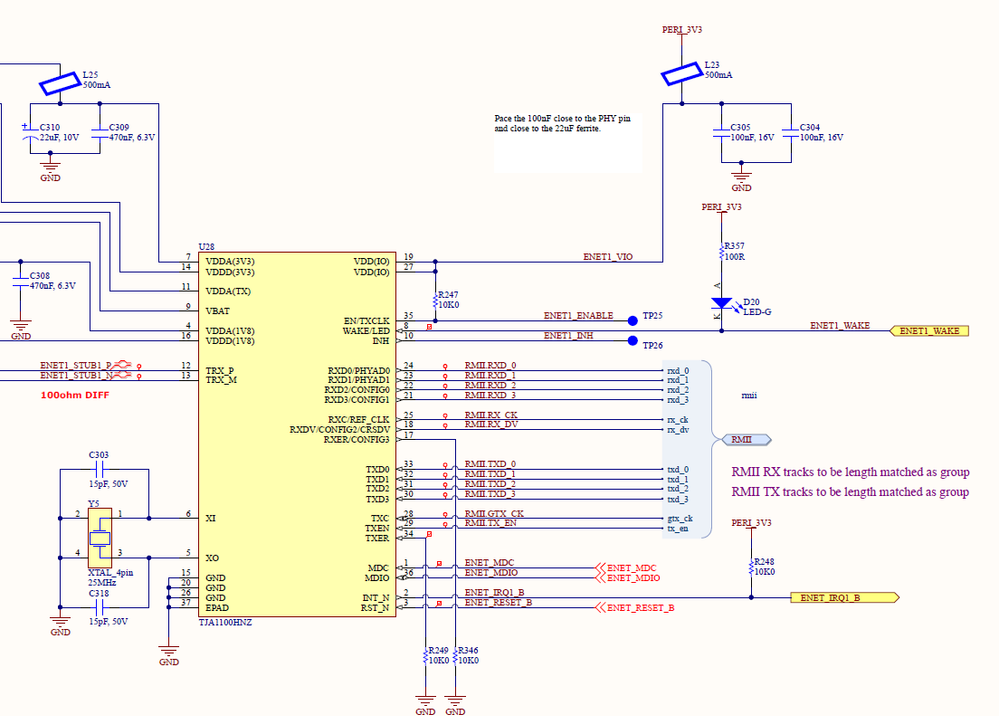

The schematics are:

DP83867:

TJA1100:

the device tree is based on the mx6sx-sdb and looks like this:

imx6sx.dtsi:

fec1: ethernet@02188000 {

compatible = "fsl,imx6sx-fec", "ethernet-phy-ieee802.3-c22";

reg = <0x02188000 0x4000>;

interrupts = <GIC_SPI 118 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 119 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6SX_CLK_ENET>,

<&clks IMX6SX_CLK_ENET_AHB>,

<&clks IMX6SX_CLK_ENET_PTP>,

<&clks IMX6SX_CLK_ENET_REF>,

<&clks IMX6SX_CLK_ENET_PTP>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "no_enet_out";

fsl,num-tx-queues=<3>;

fsl,num-rx-queues=<3>;

stop-mode = <&gpr 0x10 3>;

fsl,wakeup_irq = <0>;

phy-id=<0x2000a231>;

status = "okay";

};

fec2: ethernet@021b4000 {

compatible = "fsl,imx6sx-fec";

reg = <0x021b4000 0x4000>;

interrupts = <GIC_SPI 102 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 103 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6SX_CLK_ENET>,

<&clks IMX6SX_CLK_ENET_AHB>,

<&clks IMX6SX_CLK_ENET_PTP>,

<&clks IMX6SX_CLK_ENET2_REF_125M>,

<&clks IMX6SX_CLK_ENET_PTP>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "no_enet_out";

fsl,num-tx-queues=<3>;

fsl,num-rx-queues=<3>;

stop-mode = <&gpr 0x10 4>;

fsl,wakeup_irq = <0>;

status = "disabled";

};

custom board dtsi:

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rgmii";

phy-handle = <ðphy0>;

fsl,magic-packet;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_2_75_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

reg = <1>;

};

ethphy1: ethernet-phy@2 {

compatible = "ti,tja1101";

reg = <2>;

};

};

};

&fec2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet2>;

phy-mode = "rmii";

phy-handle = <ðphy1>;

status = "disabled";

};

pin muxing is as follows:

pinctrl_enet1: enet1grp { fsl,pins = <

MX6SX_PAD_ENET1_MDIO__ENET1_MDIO 0xa0b1

MX6SX_PAD_ENET1_MDC__ENET1_MDC 0xa0b1

MX6SX_PAD_RGMII1_TXC__ENET1_RGMII_TXC 0xa0b9

MX6SX_PAD_RGMII1_TD0__ENET1_TX_DATA_0 0xa0b1

MX6SX_PAD_RGMII1_TD1__ENET1_TX_DATA_1 0xa0b1

MX6SX_PAD_RGMII1_TD2__ENET1_TX_DATA_2 0xa0b1

MX6SX_PAD_RGMII1_TD3__ENET1_TX_DATA_3 0xa0b1

MX6SX_PAD_RGMII1_TX_CTL__ENET1_TX_EN 0xa0b1

MX6SX_PAD_RGMII1_RXC__ENET1_RX_CLK 0x3081

MX6SX_PAD_RGMII1_RD0__ENET1_RX_DATA_0 0x3081

MX6SX_PAD_RGMII1_RD1__ENET1_RX_DATA_1 0x3081

MX6SX_PAD_RGMII1_RD2__ENET1_RX_DATA_2 0x3081

MX6SX_PAD_RGMII1_RD3__ENET1_RX_DATA_3 0x3081

MX6SX_PAD_RGMII1_RX_CTL__ENET1_RX_EN 0x3081

>;

};

pinctrl_enet2: enet2grp {

fsl,pins = <

MX6SX_PAD_ENET2_RX_CLK__GPIO2_IO_8 0x10b0

MX6SX_PAD_RGMII2_TXC__ENET2_RGMII_TXC 0xa0b9

MX6SX_PAD_RGMII2_TD0__ENET2_TX_DATA_0 0xa0b1

MX6SX_PAD_RGMII2_TD1__ENET2_TX_DATA_1 0xa0b1

MX6SX_PAD_RGMII2_TX_CTL__ENET2_TX_EN 0xa0b1

MX6SX_PAD_RGMII2_RXC__ENET2_RX_CLK 0x3081

MX6SX_PAD_RGMII2_RD0__ENET2_RX_DATA_0 0x3081

MX6SX_PAD_RGMII2_RD1__ENET2_RX_DATA_1 0x3081

MX6SX_PAD_RGMII2_RD2__ENET2_RX_DATA_2 0x3081

MX6SX_PAD_RGMII2_RD3__ENET2_RX_DATA_3 0x3081

MX6SX_PAD_RGMII2_RX_CTL__ENET2_RX_EN 0x3081

>;

};

My questions are: is the configuration - especially the device tree - correct ? Why can't the mdio driver recognize the dp chip on the bus ? Even when the TJA1101 is held in reset, it still registers on the mdio bus and but mdio can't find the DP, despite the phy activity light showing the DP working. Does the FEC and mdio allow for the fact that a) both phy's are on the same mdio bus, and b) the DP is in RGMII mode and the TJA1101 is in RMII mode ?

As I understand it, the mdio driver will scan the bus for attached phy's. Does it need to be changed because the phy address of the DP is 0x1f. I also don't understand why the mdio node in the device tree is part of fec 1 but contains both phys, and fec 2 contains the second phy but it still shows up as part of fec 1:

Help is greatly appreciated, thanks

Mahtab

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

thanks for your help. The problem was in our custom board circuit design. Both phy's default to address 0x00 on the mdio bus. Every phy requires a hardware strap configuration that will set a different address when it powers up, otherwise it will default to address 0x00. At least one of the phy's should be strapped to configure a different address, but we didn't have any straps on any phy. When we added a strap to the DP83867 to give it a different address to the other phy, everything started working perfectly.

thanks,

Mahtab

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mahtab

one can try fix for custom board dtsi:

&fec2 {..

status = "disabled"; --> to okay

and check pinctrl_enet2: enet2grp {

for missing MX6SX_PAD_RGMII2_TD2,3 settings

also may be recommended to try nxp bsp from official repository

https://source.codeaurora.org/external/imx/linux-imx/tree/

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the reply.

Actually, it's fec1 which doesn't work and which we're trying to get working. Fec2 is ok, actually we don't want to use it for now and want to keep it disabled. Making fec2 "okay" doesn't help fec1 to start working.

Also, MX6SX_PAD_RGMII2_TD2,3, these lines aren't used in RMII mode, so that's why they are not in the pincntrl group.

About the nxp bsp: our linux build is based on nxp imx bsp 4.9.11-1.0.0; is the link you included above different from this ?

Thanks,

Mahtab

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mahtab

below official nxp bsp 4.9.11

it is different from fslc community bsp

GitHub - Freescale/linux-fslc at 4.9-2.0.x-imx

https://community.nxp.com/message/402940#402940

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

thanks, I checked according to your information, we are using official 4.9.11 i.MX Linux kernel.

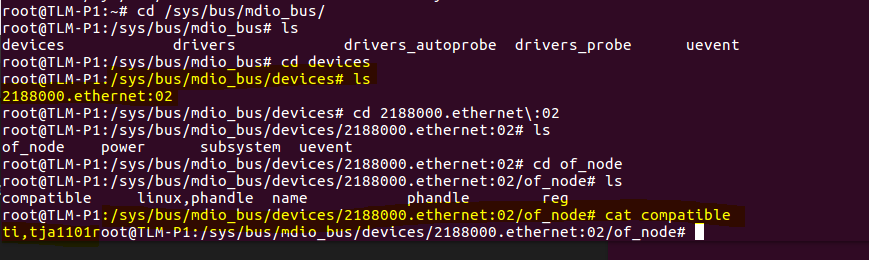

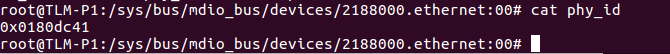

Still have the same problem: mdio bus sees wrong device, it reads id from second phy not first phy:

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-id2000-a231", "ethernet-phy-ieee802.3-c22"; /* match dp83867 phy id 0x2000a231 */

phy-connection-type = "rgmii-id";

phy-mode = "rgmii-id";

max-speed = <100>;

reset-gpios = <&gpio2 7 1>;

reset-assert-us = <1000>;

interrupt-parent = <&gpio2>;

interrupts = <9 0x02>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_2_75_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

reg = <0>

};

ethphy1: ethernet-phy@1 {

compatible = "ti,tja1101"; /* tja1101 has hardwired phy id 0x0180dc41 */

reg = <1>;

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mahtab

seems dp83867 chip is sensitive to timings, as reported on forums, one can check them

with oscilloscope and verify with datasheet

also may be useful to very if reset was implemented correctly using Figure 2. Reset Timing

http://www.ti.com/lit/ds/symlink/dp83867ir.pdf

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

After some investigation, I guess the real question that could resolve this is:

Can you have two PHY's on one FEC ? And on the same MDIO bus ( in this case MX6SX_PAD_ENET1_MDIO__ENET1_MDIO / MX6SX_PAD_ENET1_MDC__ENET1_MDC ) ?

Every time I read the registers of the PHY in the kernel ( using for example phy_read(phy_dev, REG) ), I get the phy id of the TJA1101 ( 0x180dc41), which has a DEVADDR of 0, I never see the phy id of the DP83867 ( 0x2000a231) , which has a higher DEVADDR of 0x1f. This kind of leads me to conclude that the FEC doesn't allow more than one device, and it will always pick the device with the first DEVADDR it finds on the bus.

Although, in principle, the mdio bus can cope with up to 0x1f ( 31 ) devices: the address length field for messages on the mdio bus is 5 bits.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mahtab

i.MX6SX Sabre SD has two phys and supported in linux

Schematics (1)

IMX6SOLOX-SABRESDB-DESIGNFILES

i.MX 6SoloX SABRE Development Board|NXP

[1/6] bus: Add shared MDIO bus framework - Patchwork

Best regards

igor