- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- I.mx6 LCD Power On Timing:RGB Source output starts after 6 VSyncs.

I.mx6 LCD Power On Timing:RGB Source output starts after 6 VSyncs.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.mx6 LCD Power On Timing:RGB Source output starts after 6 VSyncs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sir,

在敝司的项目中,发现LCD上电过程中有低概率的出现白屏现象。

我们目前的分析可能是与上电时序有关。

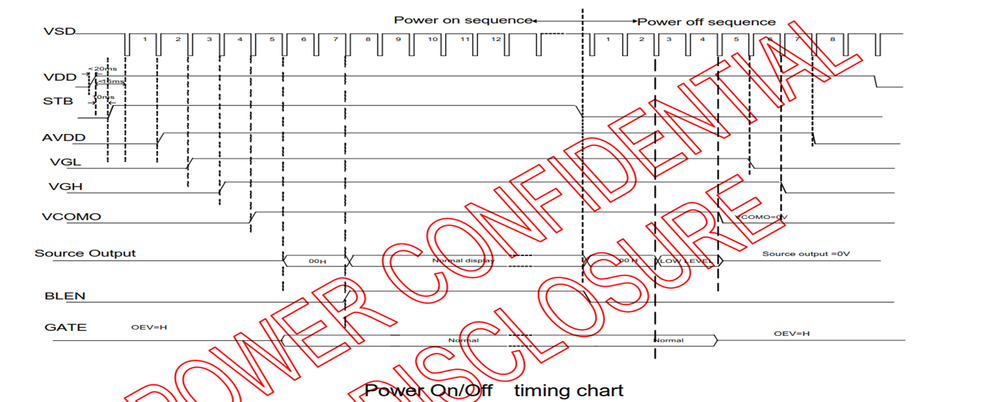

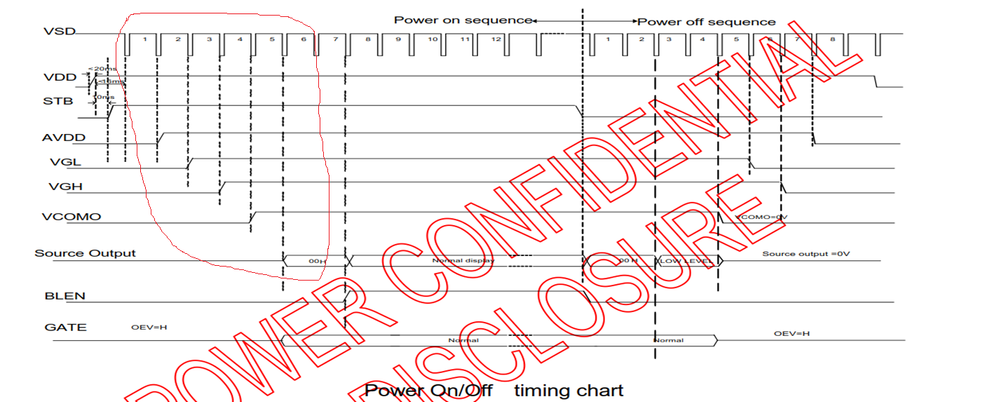

按照LCD datasheet的要求,我们需要在vs信号输出6个clk之后,再输出有效数据。如下图。

但是,实际测试发现,RGB有效数据在VS输出两个CLK之后就有了。

我们尝试修改了, ipu_disp.c文件中,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

which BSP are you using?

which i.MX6 processor are you using?

how you connect the display to i.MX6?

what is the "display-timings" setting of your display in the dtsi file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jimmy,

1) which BSP are you using?

-->i.mx6 SABRE SD board, kernel version is 3.10.31, uboot is 2013.04

2) which i.MX6 processor are you using?

-->i.mx6 solo

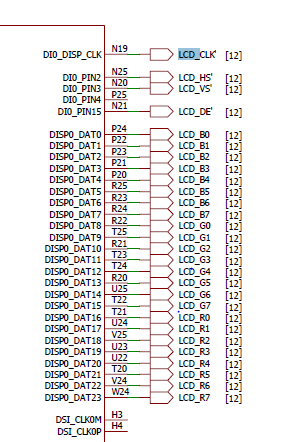

3) how you connect the display to i.MX6?

-->RGB888 ,

4) what is the "display-timings" setting of your display in the dtsi file?

in the uboot:

static struct display_info_t const displays[] = {

{

.bus = -1,

.addr = 0,

.pixfmt = IPU_PIX_FMT_RGB24,

.detect = NULL,

.enable = enable_rgb,

.mode = {

.name = "1024*600",

.refresh = 60,

.xres = 1024,

.yres = 600,

.pixclock = 19531,

.left_margin = 160,

.right_margin = 160,

.upper_margin = 23,

.lower_margin = 6,

.hsync_len = 24,

.vsync_len = 6,

.sync = FB_SYNC_EXT,

.vmode = FB_VMODE_NONINTERLACED }

}};

in the Kernel:

static struct fb_videomode lcdif_modedb_1024_600[] = {

{

/* 1024x600 @ 60 Hz , pixel clk @ 51.2MHz */

"CLAA-WVGA", 60, 1024, 600, 19531, 140, 160, 20, 12, 20, 3, //ok(51.2)

FB_SYNC_CLK_LAT_FALL, //0x40000000

FB_VMODE_NONINTERLACED, //0x0

0,},

};

Thanks.

Yonghe.Luo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why the display setting between u-boot and kernel is different?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jimmy,

我也不知道为什么会不一样,这一块是其他同事做的,我也是在刚检查代码时才发现两个地方不一样。

目前以uboot的参数为主,帮忙看一下时序上是否有问题。

谢谢!

Yonghe.Luo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You need to test the parameters of your display on your board.

For your reference, please read this App. Note about the timing setting for the display.

https://www.nxp.com/docs/en/application-note/AN3974.pdf

This document explain each parameter in very detail.

e.g. VSYNC pulse width is number of HSYNC pulses when a VSYNC signal is active. I think this is the parameter that you need to set it correct for solving your issue.

Also, please double check your display datasheet and adjust the display timing settings in kernel if needed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jimmy,

刚看了文档,这些时序是配置LCD在工作中的时序,没有发现上电过程中的时序描述?

目前,主要是想调整一下,display上电瞬间的时序,将在VS 6个信号之后,再输出有效数据。

如下图:

请帮忙看一下,如果要调整这个时序,主要是调整哪个参数?

谢谢!

Yonghe.Luo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, do you have any gpio to control the power on/off of your display? If yes, I think you can add msleep() after the power on to delay 7 VSD signals.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jimmy,

非常感谢您的回复,我这边先测试看一下。

Thanks.

Yonghe.Luo