- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- How to configure LPC43xx PLL0AUDIO frequency

How to configure LPC43xx PLL0AUDIO frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to configure LPC43xx PLL0AUDIO frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all

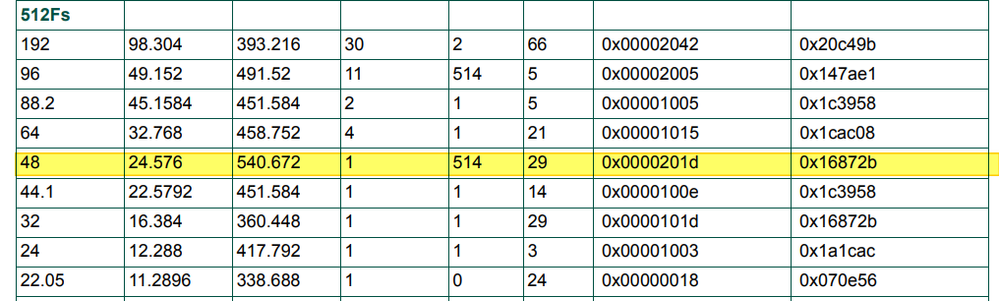

I am using om13088 development board, and try to configure clk0-pll0audio clock to 512fs where fs is 48kHz.

I am follow here to setup pll.

https://www.nxp.com/docs/en/user-guide/UM10503.pdf

Here is my configuration in board.c

static const CGU_USBAUDIO_PLL_SETUP_T audioPLLSetup = {

0x0000601D,

0x0 ,

0x0000201d ,

0x16872b,

24576000\

};

Chip_SCU_PinMuxSet (0x6, 0, (SCU_PINIO_FAST | SCU_MODE_FUNC4)); /* I2S0_RX_SCK */

Chip_SCU_PinMuxSet (0x6, 1, (SCU_PINIO_FAST | SCU_MODE_FUNC3)); /* I2S0_RX_WS */

Chip_SCU_PinMuxSet (0x3, 5, (SCU_PINIO_FAST | SCU_MODE_FUNC5)); /* I2S0_TX_SDA */

Chip_SCU_PinMuxSet (0x3, 2, (SCU_PINIO_FAST | SCU_MODE_FUNC1)); /* I2S0_RX_SDA */

Chip_SCU_PinMuxSet (0x3, 1, (SCU_PINIO_FAST | SCU_MODE_FUNC0)); /* I2S0_TX_WS */

/* set clk0 function to CLKOUT and clk0 is connected to PLL0-AUDIO */

Chip_SCU_ClockPinMuxSet(0,(SCU_MODE_FUNC1|SCU_MODE_INACT));

/* Setup base clock for CLKOUT */

Chip_Clock_SetupPLL(CLKIN_IRC, CGU_AUDIO_PLL, &audioPLLSetup);

Chip_Clock_EnablePLL(CGU_AUDIO_PLL);

Chip_Clock_SetBaseClock(CLK_BASE_OUT, CLKIN_AUDIOPLL, false, false);

The output frequency with above setting is 48Mhz

Dose anyone have ideas about how to set pll0audio?

Thanks.

Sam

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can use the Audio PLL settings calculation tool please check the following link:

Audio PLL settings calculation tool.zip

In addition check the following link:

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------