- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX7 external Bus CS1

iMX7 external Bus CS1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX7 external Bus CS1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

we use a iMX7-Colibri modul.

Currently we have a SRAM mapped in the external EIM-Bus (0x28000000-0x2FFFFFFF) - CS0 area 128MB.

It works well.

Now we like to split the area in 2 regions with CS0 and CS1 with 2 * 64 MB

CS0 (0x28000000-0x2BFFFFFF) CS1 (0x2C000000-0x2FFFFF)

I used CS0 Registers and values as a template, but I had done something wrong.

If I read from CS1 area I got the data form CS0 area. I guess there is a register value not defined.

Please can you assist me, to find the error.

I can see CS0, WR, OE,.. signals, but no CS1 signal.

I read back the register settings and the values are:

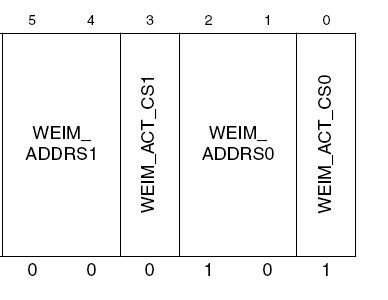

IOMUXC_GPR_GPR1: 4f40202d <-- Change to 2 * 64MB

pWEIM->CS0GCR1: 00610089

pWEIM->CS0GCR2: 00001002

pWEIM->CS0WR1: 1f6fffd3

pWEIM->CS1GCR1: 00010089

pWEIM->CS1GCR2: 00001002

pWEIM->CS1WR1: 1f6fffd3

//CS1_B mux port of EIM

pSW_PADEPDC_DATA15 = (DWORD*)Map_OALPAtoVA(IOMUXC_SW_MUX_CTL_PAD_EPDC_DATA15, 1);

*pSW_PADEPDC_DATA15 = *pSW_PADEPDC_DATA15 | 0x04; //CS1_B mux port of EIM

Can you help me.

best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manfred

according to description IOMUXC_GPR_GPR1 in Reference Manual

ADDRS[10]= 01 - 64 MByte size so for 2 * 64MB settings seems would be:

IOMUXC_GPR_GPR1: 4f40202d ==> 4f40201b

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Igor, now it works fine.