- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K82, limit access to GPIO ports by AIPS0 bridge

K82, limit access to GPIO ports by AIPS0 bridge

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K82, limit access to GPIO ports by AIPS0 bridge

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !

Do I understand right and by using AIPS0 peripheral bridge it is possible to limit access to PORTA-PORTAE

registers only ?

I can disable access with User privileges to PORTA-PORTE :

AIPS0->PACRJ = 0x44444444ul ; // Disable User access to Multiplexor Port A,B,C,D,E

But this settings dosn't have any effect to GPIOA-GPIOE ports.

As result, any task with User privileges can manipulate GPIO pins by using

GPIO_PinWrite(GPIOC, 8, 0) for example.

Is any way exists for limit access to GPIO ports ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene,

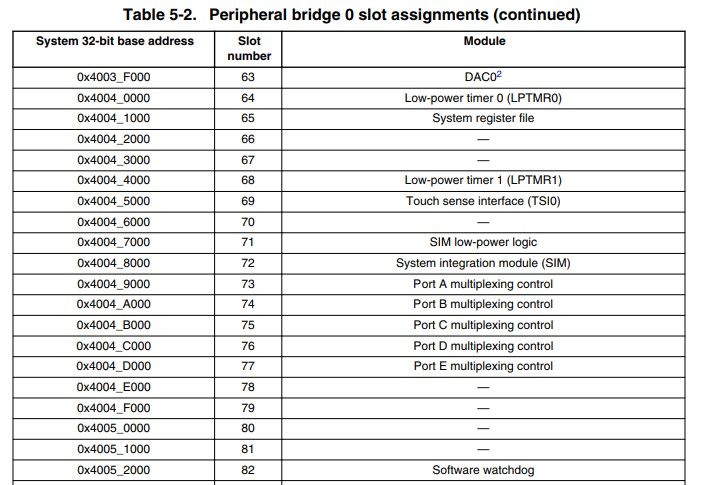

In the reference manual you can see that the slots for the PORTA, PORTB, PORTC, PORTD and PORTE are 73 to 77 respectively.

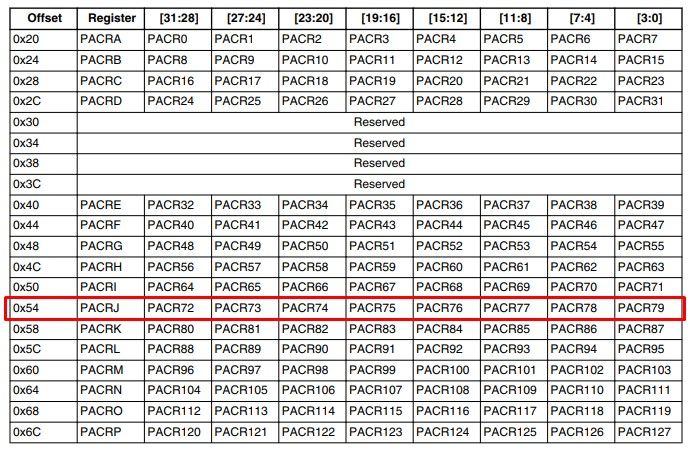

And this slots are in the register PACRJ, so you are correct on this. But you are writing to the wrong bit, lets take as an example the PORT A, that is in the slot 73.

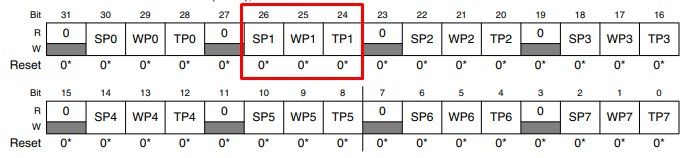

The slot 73 is located in the bits 24:27 of the register. In the next image you can see the equivalence of each bit for the slot 73.

If you want to enable the write protection you should write in the bit 25, but with the number you are passing (0x44444444) you are actually writing to the 26 bit instead of the 25. This goes for all the ports not only the PORT A.

This is why you cannot see any effect on the write protection.

Hope it helps!

Victor.

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor !

My code, what is execute line GPIO_PinWrite(GPIOC, 8, 0) running with User privilidges. (I'm using FreeRTOS what utilize K82'z MPU).

I assume if access to PORTC configured in way :

AIPS0->PACRJ = xxx7xxxx; // PACR 75 [ 19 : 16]

Any access to PORTC/GPIOC addresses should cause BusFault. But it not happens.

"

bit - 18

SP3

Supervisor Protect

Determines whether the peripheral requires supervisor privilege level for accesses. When this field is set,

the master privilege level must indicate the supervisor access attribute, and the MPRx[MPLn] control field

for the master must be set. If not, access terminates with an error response and no peripheral access

initiates.

0 This peripheral does not require supervisor privilege level for accesses.

1 This peripheral requires supervisor privilege level for accesses.

bit - 17

WP3

Write Protect

Determines whether the peripheral allows write accesses. When this field is set and a write access is

attempted, access terminates with an error response and no peripheral access initiates.

0 This peripheral allows write accesses.

1 This peripheral is write protected. -> has effect for User and Supervisor accesses

bit - 16

TP3

Trusted Protect

Determines whether the peripheral allows accesses from an untrusted master. When this bit is set and an

access is attempted by an untrusted master, the access terminates with an error response and no

peripheral access initiates.

0 Accesses from an untrusted master are allowed.

1 Accesses from an untrusted master are not allowed.

"

And I start to think if AIPS protect PORTC ( 0x4004B000) only, but not GPIOC ( 0x400FF080).

Can it be so ?

My target is to disable manipulation with GPIO pins in code what running with User privileges.

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene,

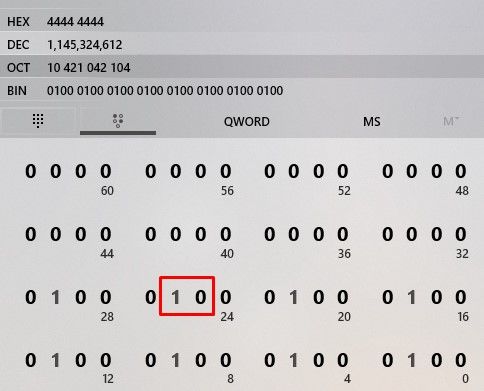

And I start to think if AIPS protect PORTC ( 0x4004B000) only, but not GPIOC ( 0x400FF080).

Can it be so ?

Yes, you are correct on this. If you go to the reference manual, chapter 64 you will see the following information.

The GPIO module does not have access protection because it is not connected to a peripheral bridge slot and is not protected by the MPU.

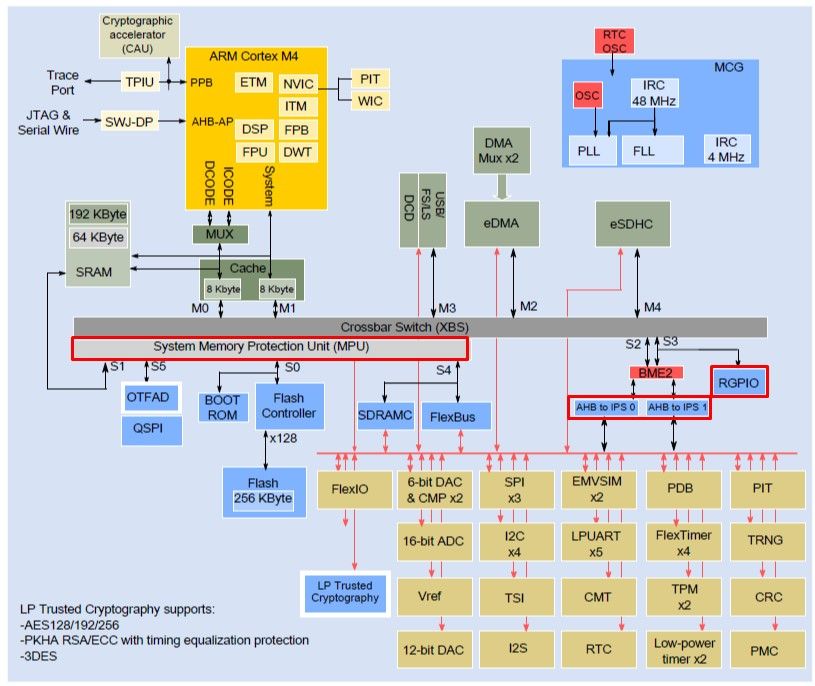

In the following image you can see that in fact the GPIO module is not connected neither to the MPU and the peripheral bridge.

Hope it helps!

Victor.

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------