- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Verifying the Built-in Self-Test (BIST) on the MPC5744P

Verifying the Built-in Self-Test (BIST) on the MPC5744P

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Verifying the Built-in Self-Test (BIST) on the MPC5744P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mr Vlna,

Please refer our discussion in Using the Built-in Self-Test (BIST) on the MPC5744P

We are using the MPC5744P CPU together with the System Basis Chip (SBC) 33907.

We are considering how to test the BIST functionality. As you mention one method would be to start the system with a low power supply level. But, what will actually happen is that the SBC will detect the low power and hold the CPU in reset?

Do you see any other methods to verify the CPU BIST?

If the CPU detects a fault during the off-line BIST it will stay in reset and after 8 seconds the SBC will enter Deep fail safe state (the system is powered off), correct?

Best Regards,

Peder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

And what you really want to do?

1. Insert a real fault into BIST testing

2. Just to test reaction on faulty BIST results

If the CPU detects a fault during the off-line BIST it will stay in reset and after 8 seconds the SBC will enter Deep fail safe state (the system is powered off), correct?

The CPU is not capable of detecting fault during off-line BIST. I works on MISR patterns. So, after BIST is finished, there is result output in MISR which is compared with expected MISR provided by NXP.

The BIST reports faults after it is finished with testing and comparing the MISR results. This is no issue as BIST is running during RESET and this is considered as safe state. No application is running.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What we really want to verify is:

- That the off-line BIST is enabled and can detect any faults.

- That the reaction on any fault is as expected, i.e. the CPU stays in reset and that the SBC eventually sets the ECU in Deep fail safe (power off).

Maybe one method to verify 1 could be to read out the BIST result registers you mention in the Application Note MPC5744P_STCU2_BIST_v0_3.pdf:

STCU2_ERR_STAT

STCU2_LBS

STCU2_LBE

STCU2_MBSL

STCU2_MBEL

I.e. if these registers show that the tests are completed successfully it could be assumed that the off-line BIST is enabled. But, to verify 2 we assume a fault has to be injected somehow...

Peder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

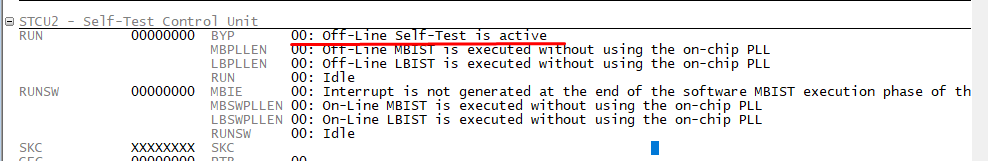

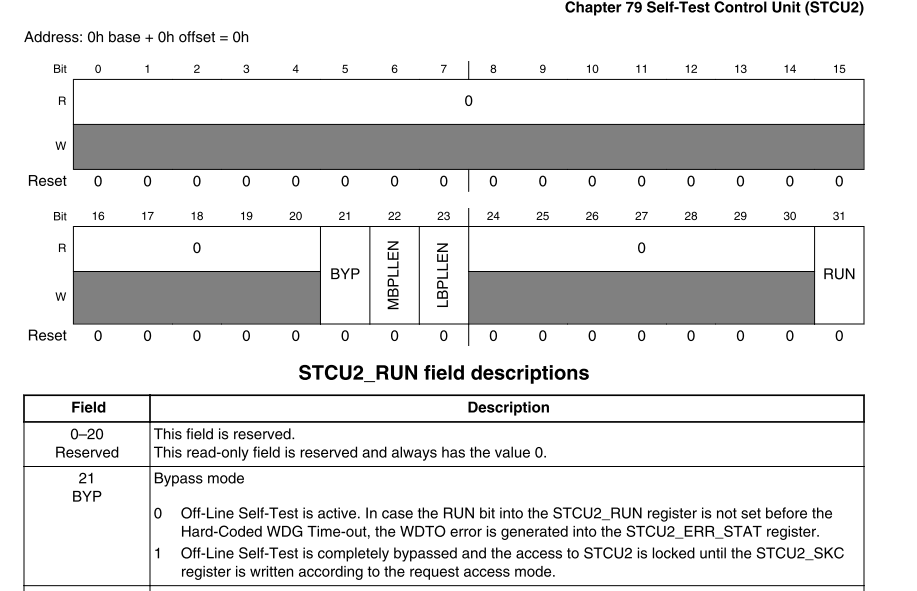

1. If BIST is enabled or not is signalized by BYP bit

You won't find this description in MPC5744P reference manual as NXP decided not to give configuration choice for MPC5744P users. But if you are interested in STCU register content you can see it in MPC5746R reference manual for example. Module is the same but number of tested partitions differs from micro to micro.

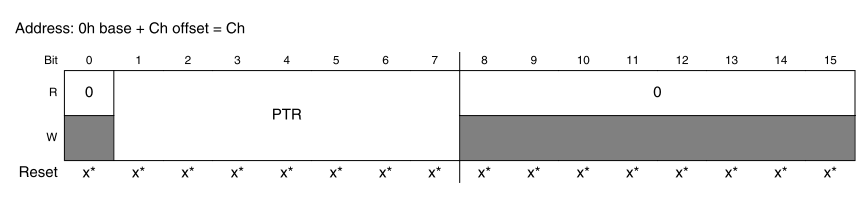

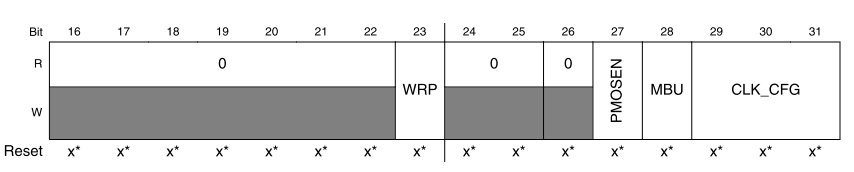

Simply enabled BIST desnt't means that it will check the device. You have to see if the STCU2_CFG pointer is set on first desired test. In this case 0x12. Because if the pointer is 0x7F then BIST is bypassed also.

So check:

1. BYP bit

2. pointer (PTR)

----------------------------------------------------------------------------------------

To check the reaction you can fake the MISR results.

For example:

Program to MISR different values then you can see in upper table. Then the BIST will report errors in ERR_STAT register.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Peter,

Thanks for your quick response. The first part above reg checking if BIST is enable or not seems quite straight forward. But, how would actually the sequence be in order to inject a fault that BIST detects? It includes on-line BIST and a sequence according the Application Note (MPC5744P_STCU2_BIST_v0_3.pdf) and example Example MPC5744P BIST On-line GHS614 would be required? Or is some simpler sequence possible to use for this purpose?

BR, Peder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Well, I have to again ask.

1. do you want to inject physical fault into BIST?

2. or you need fault in BIST for SW reaction testing?

Because if 2. is the case. Then you simply program into MISR different values from recommended ones, or shorten watchdog timeout so BIST wont have time to finish, or..... there are many ways how to fake the BIST results.

But if 1. is the case, then your only chance is to play with voltages: VDD_HV, flash, core, etc...

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

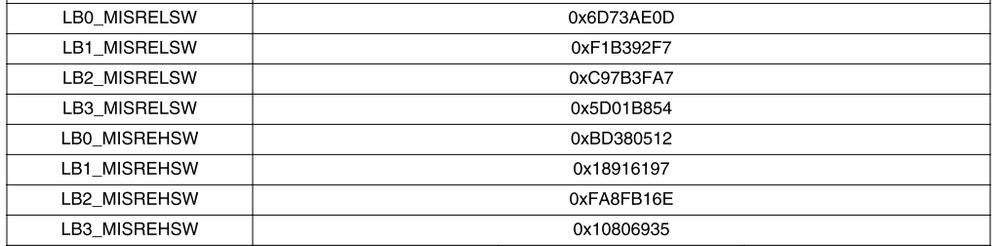

It is enough with 2. It should not be needed to inject a physical fault. But, how to actually accomplish 2? For example we can set LB0_MISRELSW to another value than 0x6D73AE0D, But, that is not enough? An on-line BIST has to be initiated?

But, actually we would like to fake a fault detected by the off-line BIST as we don't plan to use the on-line BIST.

Peder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok,

If you want to do it for offline BIST then you must modify MISR for offline BIST.

This can only be done via DCF records.

However you can also fake your SW and consider that 0 in ERR_STAT is fault state so you can test your reaction path this way.

Peter