- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Sensors

- :

- debounce counter not decrementing in orientation detection -acceleromter(FXOS8700CQ)

debounce counter not decrementing in orientation detection -acceleromter(FXOS8700CQ)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

debounce counter not decrementing in orientation detection -acceleromter(FXOS8700CQ)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have configured my FXOS8700CQ to give an interrupt at pin 1 whenever there is a change in orientation.I am receiving the interrupt at pin 1 but the interrupt flag once set is not getting cleared as debounce counter(PL_count) is not decremented can you just look into the problem,I have done all the configurations as mentioned in NXP

application note AN4068.

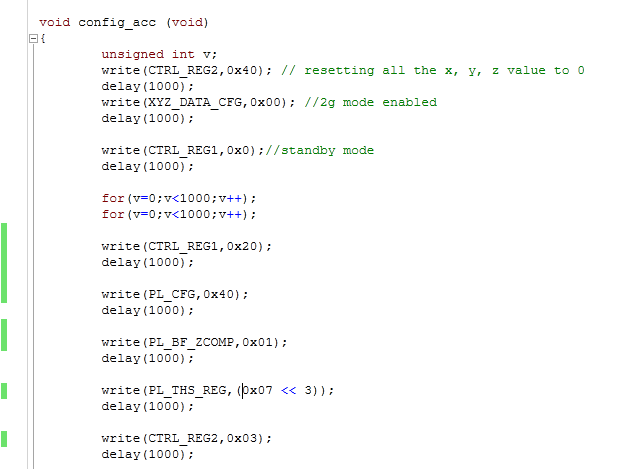

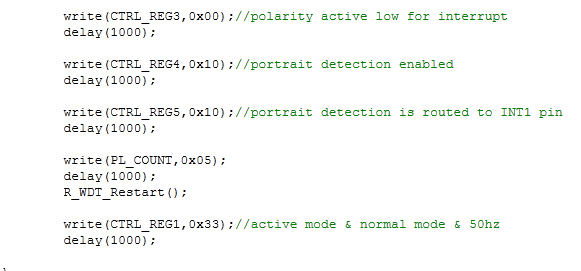

here's the configuration part of the code:

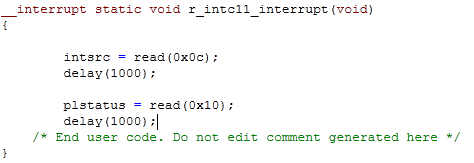

here's the interrupt service routine:

The problem is I enter the ISR and read PL status and interrupt source register but after that the debounce counter is not decrementing.

Please look into this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Naman,

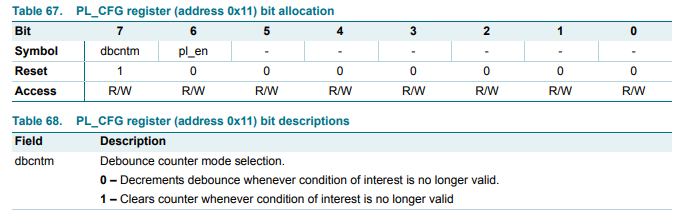

The behavior of the debounce counter can be set in the PL_CFG register using the dbcntm bit:

To clear the src_lndprt interrupt status bit in the INT_SOURCE register and consequently deassert the INT1 pin, it is necessary to read the PL_STATUS register as you are doing correctly.

However, it is also necessary to acknowledge an IRQ in your ISR by writing a logic 1 to a specific bit of your MCU. Without doing it, the interrupt flag on your MCU will remain active and then you are not able to receive any further P/L interrupts from the FXOS8700CQ.

I hope it helps.

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sir ,

I have already tried setting the dbcntm bit to 1 for clearing the counter

whenever condition of interest is no longer valid . Still the interrupt bit

is not re setting to 0 whenever orientation comes back to it's original

position.

I hope you will look into this problem.

Regards

Naman Sharma