- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Unmatch about DDR DDR Output Driver Average Impedance for i.MX53

Unmatch about DDR DDR Output Driver Average Impedance for i.MX53

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all

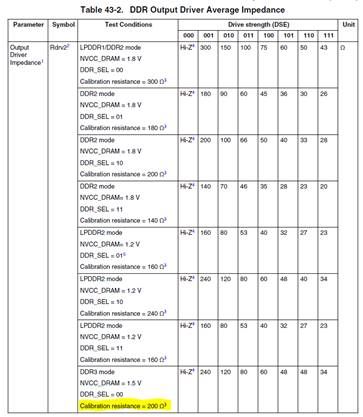

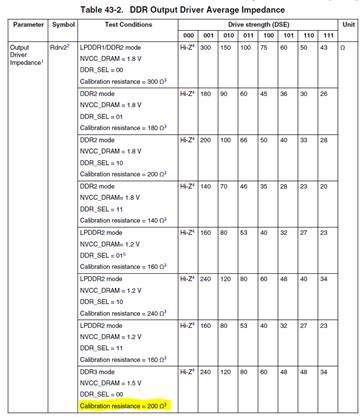

I have questions about DDR calibration resistance in Output Driver Average Impedance for i.MX53.

As it mentioned in following thread, the Table 43-2 and 43.3.454 unmatched and we have same question.

But there didn't answer the thread.

https://community.nxp.com/thread/328744

Q1.

Table 43-2 does not describe the DSE value when it set DDR3 dde_sel = 01.

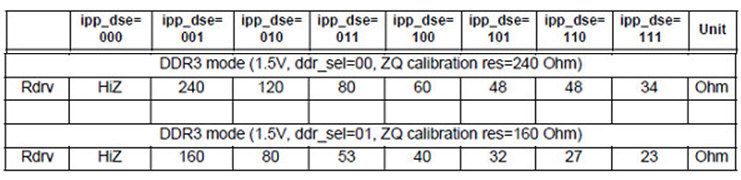

Refer to 43.3.454 IOMUXC_SW_PAD_CTL_GRP_DDR_TYPE and it is explained as "NVCC_EMI_DRAM = 1.5 V +/- 5% (DDR 3), ddr_sel = '' 01: 160 Ohm '

In the case of dde_sel = 01 setting of DDR3, is the value of DSE the same as DDR_SEL = 01/11 of LPDDR 2 mode in Table 43-2 ?

Q2.

If Q1 is not same, could you provide a DSE value when it set DDR3 dde_sel = 01 ?

Q3.

We think that the calibration resistance which is shows in yellow line is wrong.

Because there are no settings in Table 43.3.454.

The correct calibration resistance is 200 Ohm. Am I correct ?

Ko-hey

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ko-hey

>Q1.2

please refer to below description

>Q3

correct is 240 Ohm

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ko-hey

>Q1.2

please refer to below description

>Q3

correct is 240 Ohm

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The table you quote lists resistances of 240, 120, 80, 60, 48, 48 and 34.

In the thread quoted from the original post in this thread, I pointed out the above values are wrong and gave corrections. That was back in August 2014. I had to look in the i.MX6 manual to get the correct values (which are 48 and 40).

i.MX53 Reference Manual Errors, is there a list?

I would suggest the original poster do the same. When in doubt, read a newer manual for a different product.

In the above thread, four years ago, gusarambula reported these bugs, but said it might take "some time" for these to be fixed. He also said these postings are likely to be the only places you'll see these sort of corrections.

Tom