- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Probe point to measure a timing of uSDHC

Probe point to measure a timing of uSDHC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello community,

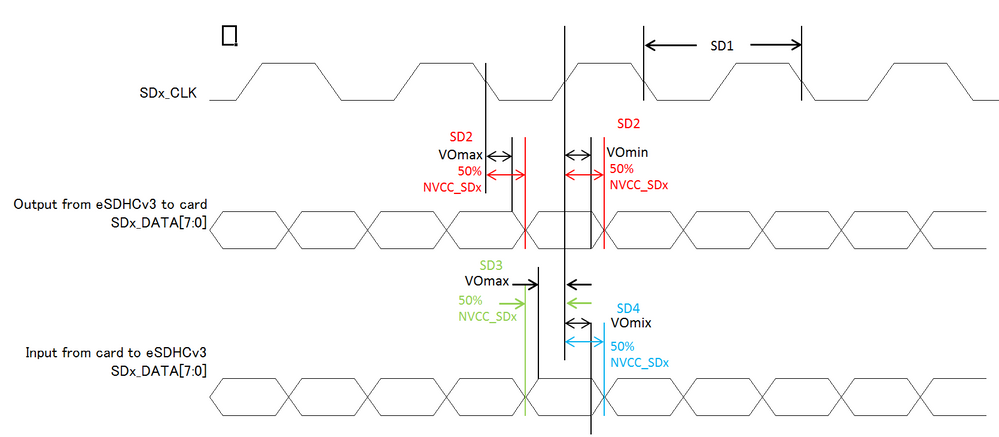

About Figure 40 and Table 51 in Datasheet of IMX6DQPAEC rev2,

Which point does it measured from/to?

In Figure 40, it seems that

SD2: uSDHC Output Delay from "50% of SD_CLK" to "Voh max value".

SD3: uSDHC Input Setup Time from "Voh max value" to "50% SD_CLK"

SD4: uSDHC Input Hold Time from "50% SD_CLK" to "Vol mix value"

Or from "50% SD_CLK" to "50% SD_DATA"?

Which is a correct answer?

Best regards,

Ishii.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Ishii!

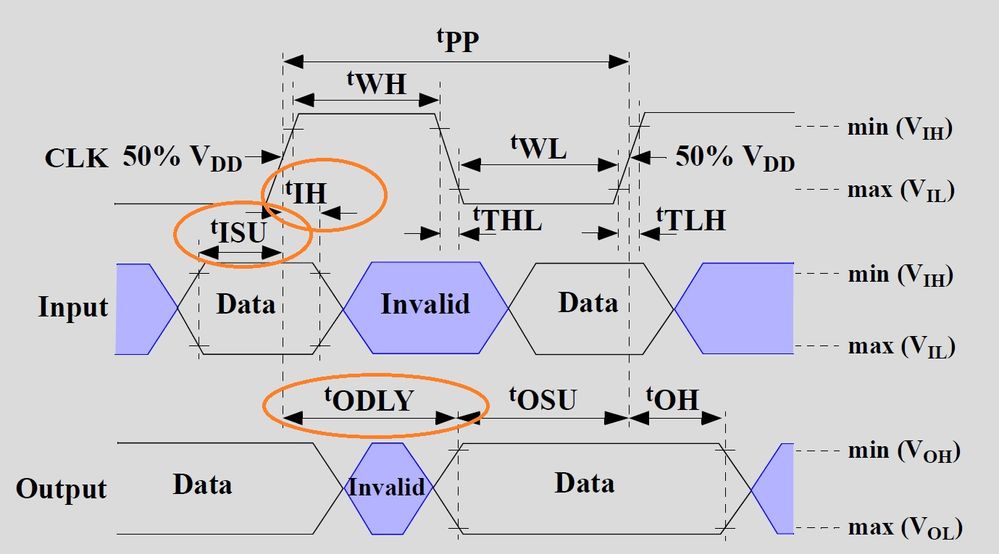

For DDR mode:

CLK timing is measured at 50% of VDD.

Inputs CMD, DAT rise and fall times are measured by min (VIH) and max (VIL),

and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL).

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

SD2 is Output Delay from "50% of SD_CLK" to "Voh min value".

SD3 is Input Setup Time from "Vih min value" to "50% SD_CLK".

SD4 is Input Hold Time from "50% SD_CLK" to "Vih min value".

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Thank you for your quick response.

How about DDR mode in eMMC?

Figure you attached is a single mode one.

Is it same in DDR mode of eMMC?

We hope to know it because timing is very critical for DDR access.

Best regards,

Ishii.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Ishii!

For DDR mode:

CLK timing is measured at 50% of VDD.

Inputs CMD, DAT rise and fall times are measured by min (VIH) and max (VIL),

and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL).

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Thank you for your answered.

I will answer it to my customer.

Best regards,

Ishii.