- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Explaining S32K1xx Pad Types

Explaining S32K1xx Pad Types

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Explaining S32K1xx Pad Types

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I need some more information related to the different S32K148 pad types.

From the document "S32K148_IO_Signal_Description_Input_Multiplexing" Pinout sheet I see the following pad names for each pin.

- p_gnd_mv

- p_io_5ma_mv

- p_io_20ma_mv

- p_io_ae_mv

- p_io_quadspi_mv

- p_io_rst_mv

- p_pwr_mv

- p_vdda_mv

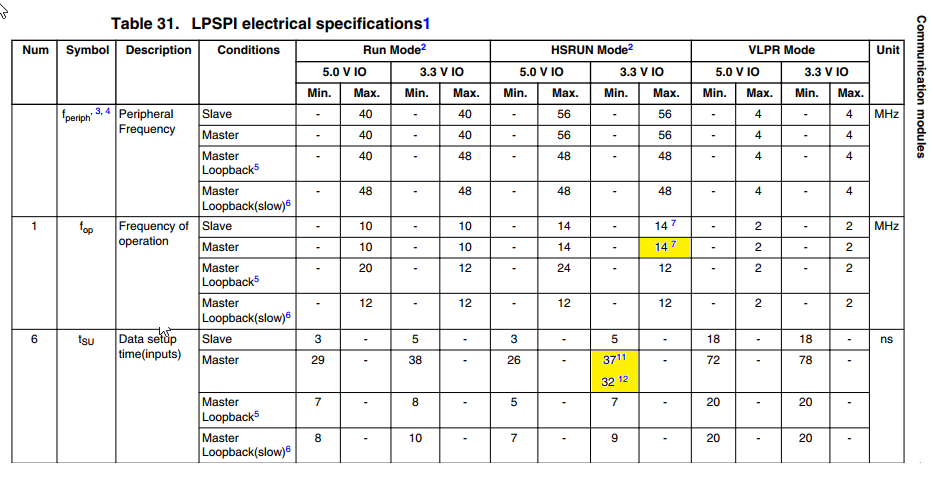

In the S32K1xx datasheet (Rev 6 01/2018) Table 31 it has the following note.

7. This is the maximum operating frequency (fop) for LPSPI0 with medium PAD type only. Otherwise, the maximum operating frequency (fop) is 12 Mhz

11. Maximum operating frequency (fop ) is 12 MHz irrespective of PAD type and LPSPI instance

12. Applicable for LPSPI0 only with medium PAD type, with maximum operating frequency (fop) as 14 MHz

How do I map "medium PAD type" to the pad names above?

This all relates to the maximum frequency and minimum data setup time for LPSPI0 in master mode using the following pins

- PTD16 : SPI0_SDI

- PTD15 : SPI0_SCK

- PTB5 : SPIO_CS

- PTB4 : SPIO_SDO

Is the maximum frequency 14MHz or 12MHz in HSRUN?

Is the minimum data setup time 37ns or 32ns in HSRUN?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stephan,

For example, you can configure the pin PTB5 for the LPSPI0 like below.

Should be used GPIO-HD pins (specified in S32K148 IO_Signal_Description_Input_Multiplexing.xlsx) and set PCR_DSE = 1.

PORTB->PCR[5] &= ~PORT_PCR_MUX_MASK; /* Set MUX=0 temporarily */

PORTB->PCR[5] |= PORT_PCR_MUX(4) | /* MUX=4: Select LPSPI0_PCS0 on PTB5 */

PORT_PCR_DSE_MASK; /* DSE=1: High drive strength is configured */

The maximum operating frequency HSRUN at 3V3 VDD is 14MHz. In that case is minimum data setup time 32ns.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

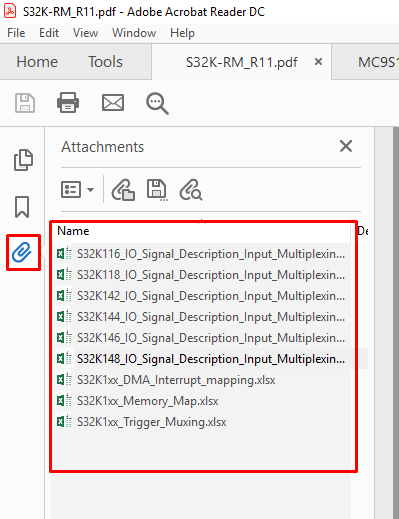

How to get the IO Signal Description Input Multiplexing sheet for S32K148 microcontroller?

S32K148 reference doc is not attached with IO Signal Description Input Multiplexing sheet for S32K148 microcontroller

Hello Diana Batrioa

Can you help me to get the document as mentioned above?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please, download the Reference Manual and open it in the PC

https://www.nxp.com/docs/en/reference-manual/S32K-RM.pdf

the document can be seen in the attachment:

I hope it helps.

BR,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana

Sorry to report. In the suggested doc, the full description of pad description is blocked.

Regards,

Kanakaraju

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

Thanks for your reply.

From your response it seems like only the SPI_CS pin (PTB5) in this case needs PCR_DSE set to 1.

Is this required for the SPI_SCK pin, PTD15 in this case?

Does SPI_SCK require any special configuration outside configuring PORT_PCR_MUX = 4?

As well in our application we are controlling the SPI0 Chip Select manually, configuring it as a GPIO, PORT_PCR_MUX = 1. (see code below)

PORTB->PCR[5] = PORT_PCR_MUX(1); // CS

PTB->PDDR |= (1 << 5); // set as output#define FLASH_CHIP_SELECT PTB->PCOR = (1 << 5)

#define FLASH_CHIP_DESELECT PTB->PSOR = (1 << 5)

Does using the pin, PTB5, in this way still require PCR_DSE set to 1?

Is the maximum operating frequency for LPSPI0 in HSRUN at 3V3 VDD still 14MHz?

Thanks,

Stephan