- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5777C EBI constraints

MPC5777C EBI constraints

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are in the process of allocating the CPU pins of our board. We want to use the following EBI CS:

CS0: 32bits muxed

CS1: 16bits non-muxed

CS2: 16bits non-muxed

CS3: 32bits muxed

We also want to use TEA signal.

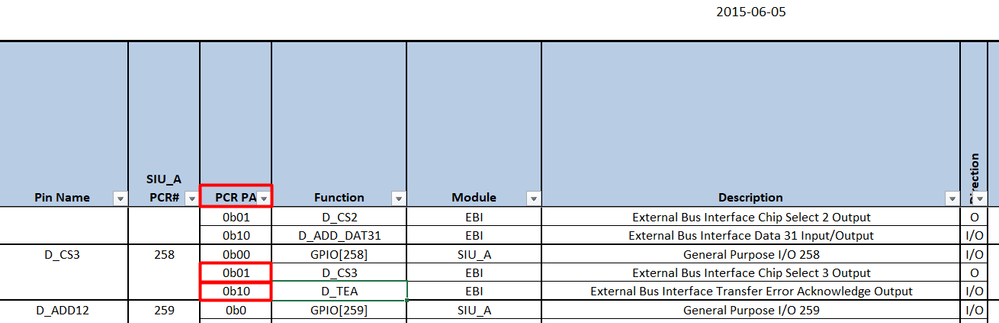

1) We don't see how CS2 can be used in muxed mode since the same pin is used both for CS2, Addr31 and Data31...

2) Can we used both CS3 and TEA? It seems not since they are on the same pin.

3) Would it be possible to use CS0 and CS1 to drive 4 chips selects through an external decoder?

We do not understand why there are such constraints limitating the use of EBI module...

Thanks!

Étienne

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

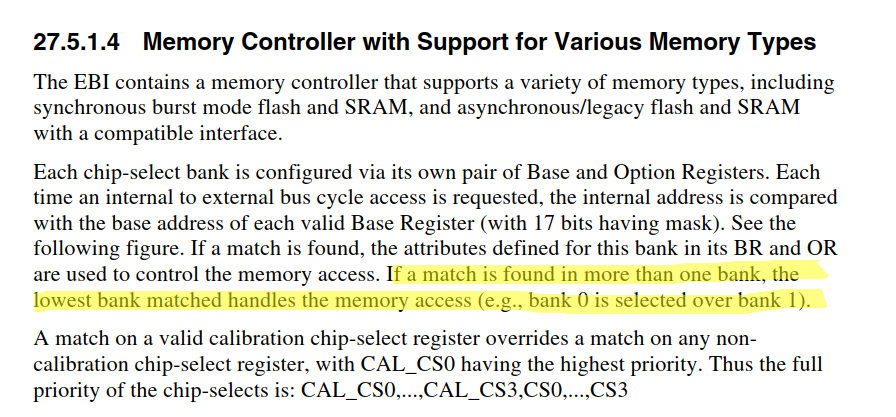

Hi, in such configuration I see significant issue I am describing here, section 7:

As it is routed same way on MPC5777C, using of muxed and non-muxed mode is not the best way. However you can always use muxed mode, can't you? Combination of muxed 16-bit and muxed 32-bit is not an issue.

1) It is basically the same case - D_CS2 is the primary function. Secondary function is EBI data only in non-mux mode and address/data in mux mode. You can use D_CS2 as chip select only for 'Non-muxed 16-bit mode' (because in this case you don't need Address 31) or 'Muxed 16-bit mode (EBI_MCR[D16_31]=0)'

2) No, it is again the same problem.

3) No, it is not possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, in such configuration I see significant issue I am describing here, section 7:

As it is routed same way on MPC5777C, using of muxed and non-muxed mode is not the best way. However you can always use muxed mode, can't you? Combination of muxed 16-bit and muxed 32-bit is not an issue.

1) It is basically the same case - D_CS2 is the primary function. Secondary function is EBI data only in non-mux mode and address/data in mux mode. You can use D_CS2 as chip select only for 'Non-muxed 16-bit mode' (because in this case you don't need Address 31) or 'Muxed 16-bit mode (EBI_MCR[D16_31]=0)'

2) No, it is again the same problem.

3) No, it is not possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, in my case I would move the 16bits CS to muxed mode. But wouldn't I lose performance?

Also, just to understand, the problem with mixing muxed and non-muxed CS is about D_ADD and D_ADD_DAT pins which have an excludive PCR setting, right? All the other pins would support that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There will be minimal performance impact as address multiplexing access only add 1 cycle to small accesses. All other accesses have the same length as address is placed onto data bus when /TS line is asserted (in non-muxed there is a dead cycle there).

Yes, problem is only that muxed addr/data lines and non-muxed address lines are routed to the same pins and their functionality are being selected by particular PCR register setting (primary or alternative function).

Software workaround would be to reconfigure PCR regs before every access to non-muxed memory and

after access change PCR regs back i.e. 16 PCR writes before access and 16 PCR writes after access.

Surely better solution would be to use muxed access for all device connected to EBI, besides you have already installed latch devices on the board..