- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Software Forums

- :

- S32 Design Studio

- :

- How to set SPLL clock to 80MHz?

How to set SPLL clock to 80MHz?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to set SPLL clock to 80MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

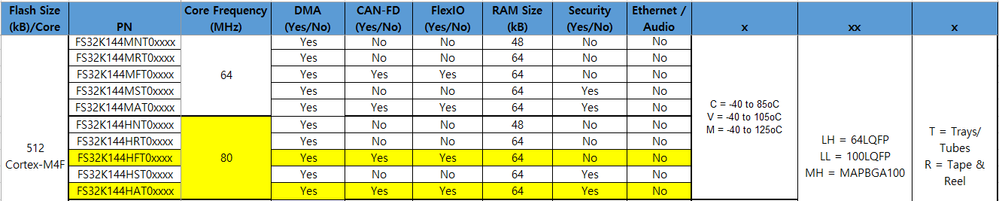

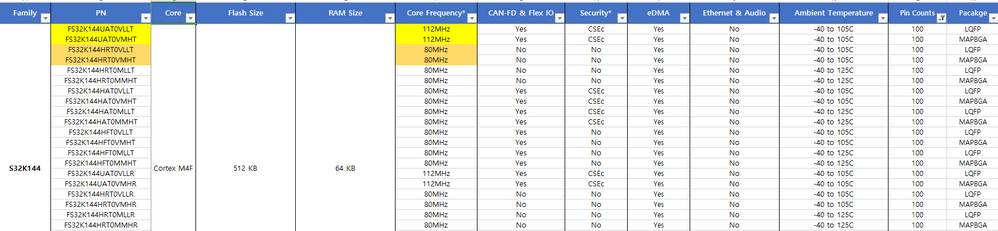

I would like to use FS32K144HFT0xxxx MCU.

The MCU's core frequency is 80MHz.

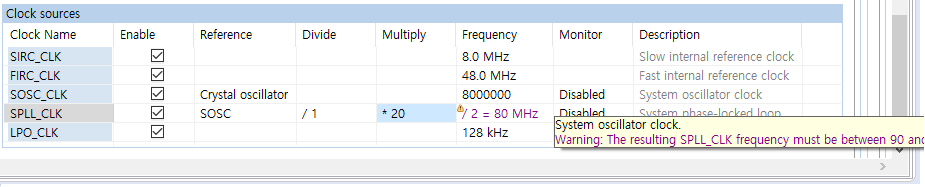

So I try to set SPLL clock to 80MHz with SKD_S32K14x_09 in S32 design studio for ARM.2018.R1

But I could not set SPLL clock to 80MHz, because of below warning.

Is it possible to set SPLL clock to 80MHz?

If it is possible, how to set 80MHz?

Thanks and best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

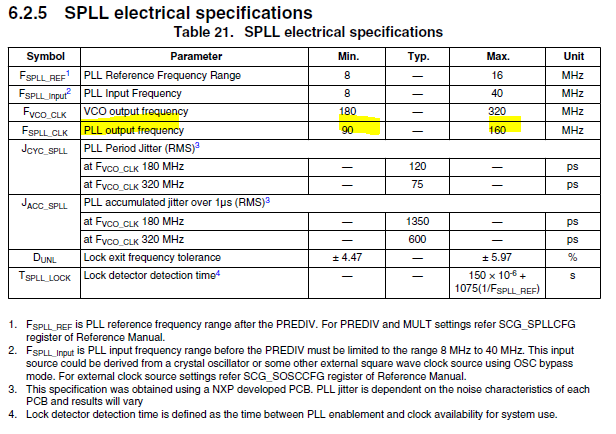

based on this AN - https://www.nxp.com/docs/en/application-note/AN5408.pdf the supported range for SPLL is 90-160 MHz.

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jiri,

As your comment, SPLL frequency spec is below.

In case of FS32K144HFT0xxxx MCU, Core frequency is 80MHz.

If I set the SPLL clock of FS32K144HFT0xxxx to 90MHz, Is there any problem in operation?

Best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the 90MHz is in range So I'm not expecting any issues.

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jiri,

Thanks for your help.

I have one more question.

I think that the means that core frequency is 80MHz means the configurable max frequency is 80MHz.

Do I misunderstand?

Best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Byungiju,

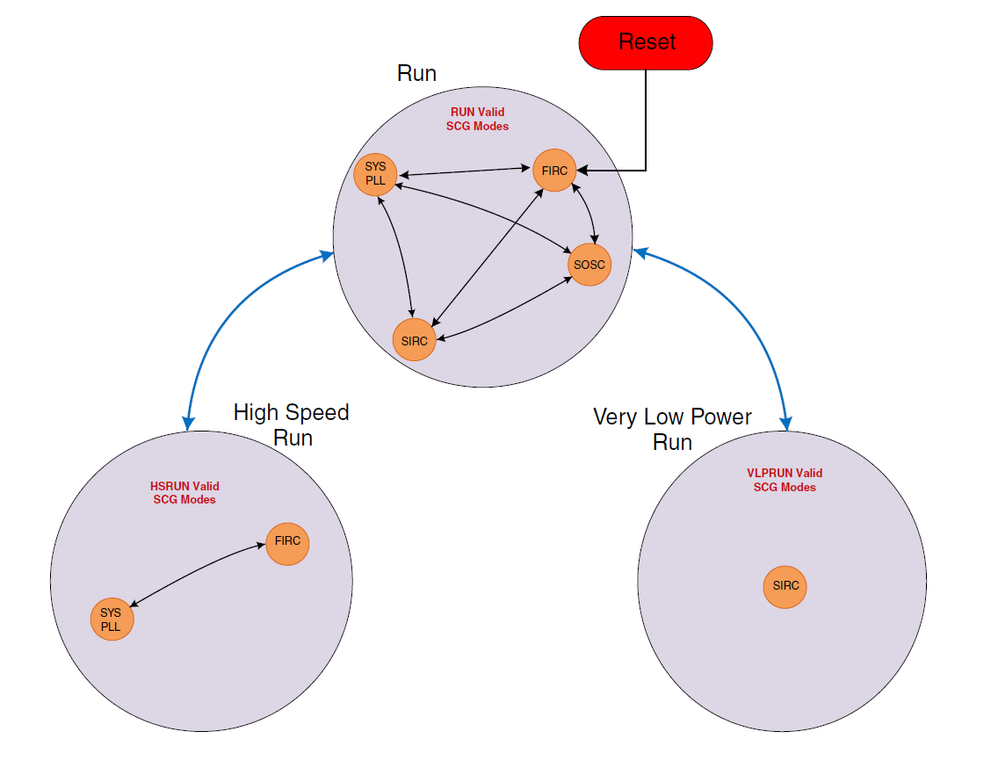

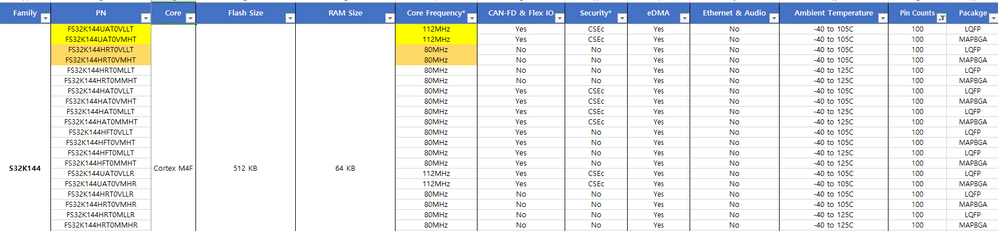

The core clock depends on Run mode. In HSRUN - the core clock should be 112MHz, in normal RUN 80MHz and so on. Please look at chapter 27-30 in reference manual - page 533+ https://www.nxp.com/docs/en/reference-manual/S32K-RM.pdf

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jiri

There are F32K144UAT0VLLT MCU that core frequency is 112MHz and F32K144HRT0VLLT that core frequency is 80MHz.

Both of MCUs can set the SPLL to 90MHz?

If Core frequency is not SPLL requency, What is core frequency?

Thanks and best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I didn't find any SPLL limitations info for HRT0VLLT variant. So - let's summarize it:

The SPLL clock source is frequency of Oscilator - for example 8MHz. SPLL output range is 90-160MHz -taken from FOSC by dividers/multipliers.

SPLL output is source for Core clock. You need to use dividers/multipliers in way to satisfy the max allowed core clock for HSRUN. That is how I understand it.

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jiri,

Thanks for your reply.

I will repeat the following questions for clarification.

1. What does the Core Frequency in the EXCEL table below mean?

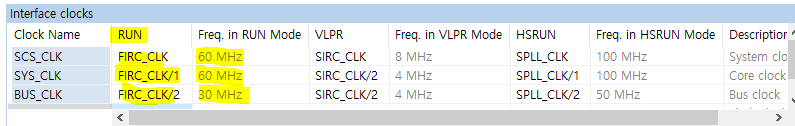

2. If the core frequency is the frequency of normal RUN mode, how do you set it to 80MHz? (If you set it to FIRC, it is max. 60Mhz.)

Best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The 80MHz in the table means that ARM core can run on 80MHz or less.

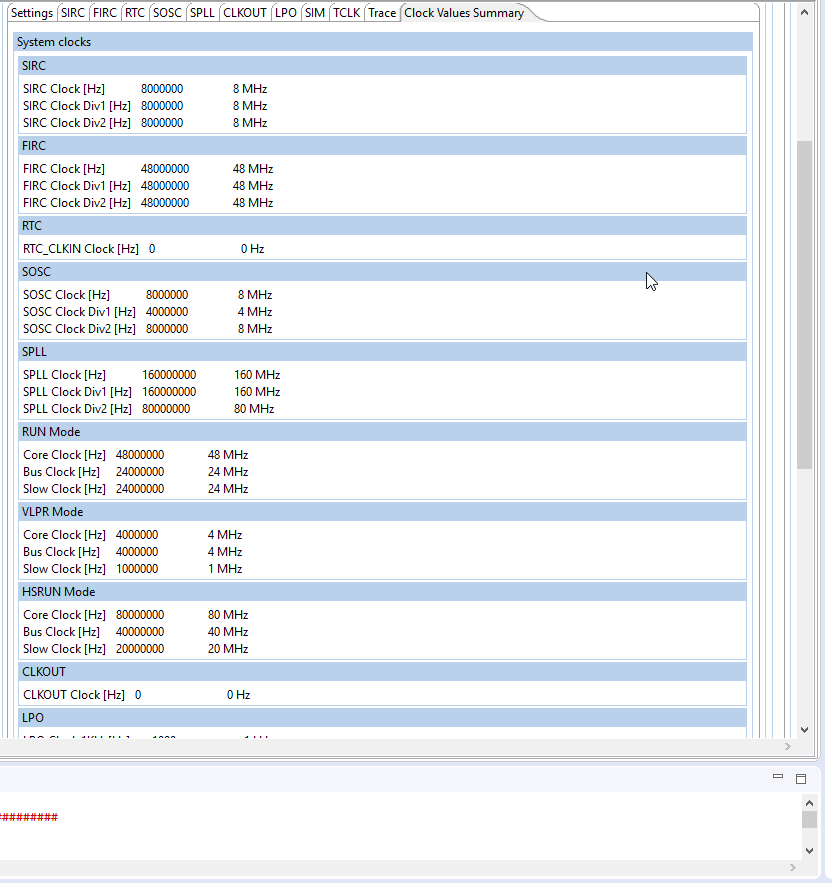

can you share your project? I'm not able set for example FIRC to 60MHz on my project. To check final values is better look at the Clock values summary page:

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Jiri,

Thanks for your help.

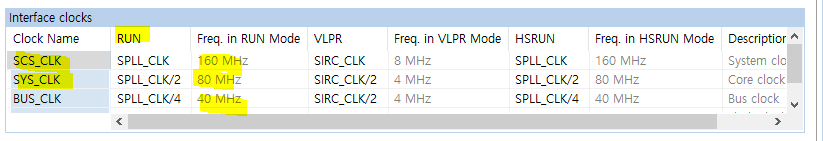

As you do, I set SYS_CLK of RUN mode to 80MHz.

Best regards,

Byungju.