- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- EEPROM Emulation Driver / Standard Software Driver v1.1.0

EEPROM Emulation Driver / Standard Software Driver v1.1.0

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

EEPROM Emulation Driver / Standard Software Driver v1.1.0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried getting the EEE_Driver_v1.3.0 to work, but there seems to be some problems. So...

I am trying to implement the Eeprom Emulation driver for the MPC5746C.

I'm not sure about a few things.

1. I don't see any support for the MPC5746C. Perhaps I just have to modify one of the other examples to suit the MPC5746C?

2. I think I have to use the VLE c-array driver

3. I am using the S32 compiler. I don't see any support for that either. I am getting errors in DCache.c

Anything else I am not aware of would be greatly appreciated to get this to work.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

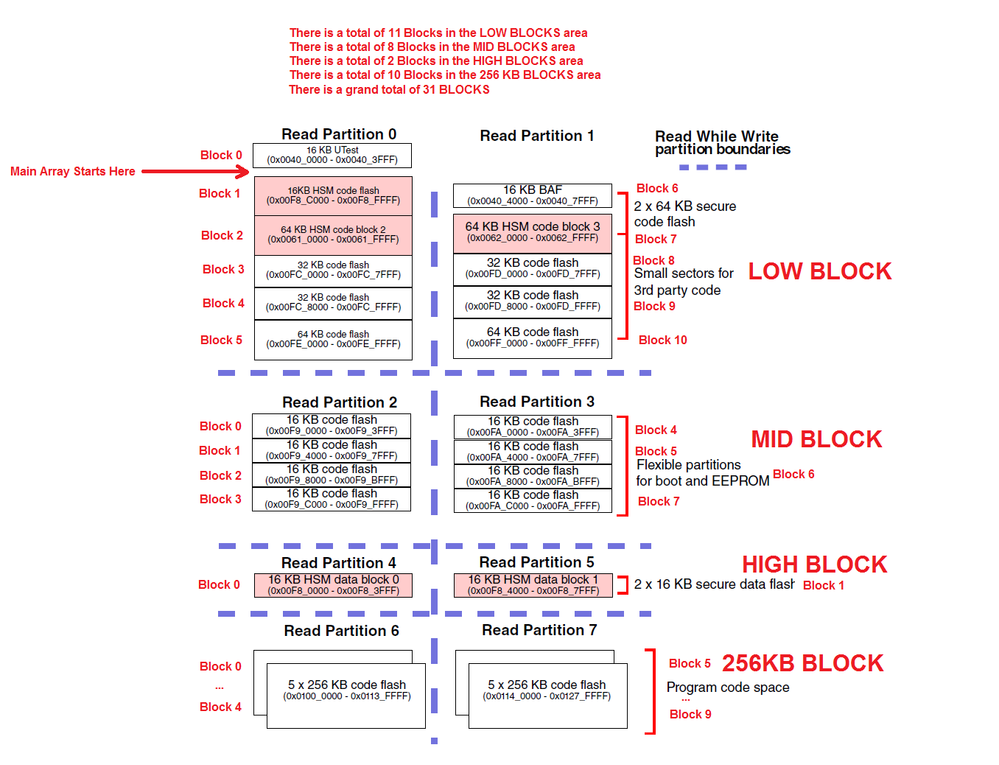

This is for reference

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From what I gather, the MCP5746C uses the e200z4 core, which from wikipedia states that it has no data cache. Also, it uses the VLE instruction set.

e200z4[edit]

The e200z4 has a five-stage, dual-issue pipeline with a branch prediction unit, a 16 entry MMU, signal processing extension (SPE), a SIMD capable single precision FPU and a 4 Kilobyte 2/4-way set associative instruction L1 cache(Pseudo round-robin replacement algorithm). It has no data cache. It can use the complete 32-bit PowerPC ISA as well as the VLE instructions. It uses a dual 64-bit bus AMBA 2.0v6 interface. The load/store unit is pipelined, has a 2-cycle load latency and supports throughput of one load or store operation per cycle.

Depending on the derivative may support SPE or LSP.

I updated the 3 files

block_mpc57xx.c, block_mpc57xx.h and c55flash_mpc57xx.h for the MPC5746C

/************************************************************************

* (c) Copyright Freescale Semiconductor, 2012-2014 *

* All Rights Reserved *

*************************************************************************

*************************************************************************

* *

* Standard Software Driver for C55 *

* *

* FILE NAME : block_mpc57xx.c *

* DATE : 09.19.2014 *

* *

* AUTHOR : FPT Team *

* E-mail : r56611@freescale.com *

* *

************************************************************************/

/******************************* CHANGES ********************************

1.0.0 12.29.2011 FPT Team Initial Version for RTM version

***********************************************************************/

#include "Flash_Driver/include/ssd_types.h"

#include "block_mpc57xx.h"

/* Block start addresses */

const UINT32 BLOCK_START_ADDRS[NUM_BLOCK_ALL] =

{

/* LOW - (Partitions 0 and 1) */

/* Partition 0 */

0x00400000, /* (Block 00) - UTest */

0x00F8C000, /* (Block 01) - 16KB HSM Code Flash */

0x00610000, /* (Block 02) - 64KB HSM code block 2 */

0x00FC0000, /* (Block 03) - 32KB code flash */

0x00FC8000, /* (Block 04) - 32KB code flash */

0x00FE0000, /* (Block 05) - 64KB code flash */

/* Partition 1 */

0x00404000, /* (Block 06) - BAF */

0x00620000, /* (Block 07) - HSM code block 3 */

0x00FD0000, /* (Block 08) - 32KB code flash */

0x00FD8000, /* (Block 09) - 32KB code flash */

0x00FF0000, /* (Block 10) - 64KB code flash */

/* MID - (Partitions 2 and 3) */

/* Partition 2 */

0x00F90000, /* (Block 11) - 16KB Code Flash */

0x00F94000, /* (Block 12) - 16KB Code Flash */

0x00F98000, /* (Block 13) - 16KB Code Flash */

0x00F9C000, /* (Block 14) - 16KB Code Flash */

/* Partition 3 */

0x00FA0000, /* (Block 15) - 16KB Code Flash */

0x00FA4C00, /* (Block 16) - 16KB Code Flash */

0x00FA8000, /* (Block 17) - 16KB Code Flash */

0x00FAC000, /* (Block 18) - 16KB Code Flash */

/* HIGH - (Partitions 4 and 5) */

/* Partition 4 */

0x00F80000, /* (Block 19) - HSM data block 0 */

/* Partition 5 */

0x00F84000, /* (Block 20) - HSM data block 1 */

/* LARGE - (Partitions 6 and 7) */

0x01000000, /* (Block 21) - 256KB Code Flash */

0x01040000, /* (Block 22) - 256KB Code Flash */

0x01080000, /* (Block 23) - 256KB Code Flash */

0x010C0000, /* (Block 24) - 256KB Code Flash */

0x01100000, /* (Block 25) - 256KB Code Flash */

0x01140000, /* (Block 26) - 256KB Code Flash */

0x01180000, /* (Block 27) - 256KB Code Flash */

0x011C0000, /* (Block 28) - 256KB Code Flash */

0x01200000, /* (Block 29) - 256KB Code Flash */

0x01240000 /* (Block 30) - 256KB Code Flash */

};

/* Block end addresses */

const UINT32 BLOCK_END_ADDRS[NUM_BLOCK_ALL] =

{

/* LOW - (Partitions 0 and 1) */

/* Partition 0 */

0x00403FFF, /* (Block 00) 16 KB UTest */

0x00F8FFFF, /* (Block 01) 16KB HSM Code Flash */

0x0061FFFF, /* (Block 02) 64KB HSM code block 2 */

0x00FC7FFF, /* (Block 03) 32KB code flash */

0x00FCFFFF, /* (Block 04) 32KB code flash */

0x00FEFFFF, /* (Block 05) 64KB code flash */

/* Partition 1 */

0x00407FFF, /* (Block 06) BAF */

0x0062FFFF, /* (Block 07) HSM code block 3 */

0x00FD7FFF, /* (Block 08) 32KB code flash */

0x00FDFFFF, /* (Block 09) 32KB code flash */

0x00FFFFFF, /* (Block 10) 64KB code flash */

/* MID - (Partitions 2 and 3) */

/* Partition 2 */

0x00F93FFF, /* (Block 11) 16KB Code Flash block (Eeprom 0)*/

0x00F97FFF, /* (Block 12) 16KB Code Flash block (Eeprom 1)*/

0x00F9BFFF, /* (Block 13) 16KB Code Flash block (Eeprom 2)*/

0x00F9FFFF, /* (Block 14) 16KB Code Flash block (Eeprom 3)*/

/* Partition 3 */

0x00FA3FFF, /* (Block 15) 16KB Code Flash block (Eeprom 4)*/

0x00FA7FFF, /* (Block 16) 16KB Code Flash block (Eeprom 5)*/

0x00FABFFF, /* (Block 17) 16KB Code Flash block (Eeprom 6)*/

0x00FAFFFF, /* (Block 18) 16KB Code Flash block (Eeprom 7)*/

/* HIGH - (Partitions 4 and 5) */

/* Partition 4 */

0x00F83FFF, /* (Block 19) HSM data block 0 */

/* Partition 5 */

0x00F87FFF, /* (Block 20) HSM data block 1 */

/* LARGE - (Partitions 6 and 7) */

0x0103FFFF, /* (Block 21) 256KB Code Flash block0 */

0x0107FFFF, /* (Block 22) 256KB Code Flash block0 */

0x010BFFFF, /* (Block 23) 256KB Code Flash block0 */

0x010FFFFF, /* (Block 24) 256KB Code Flash block0 */

0x0113FFFF, /* (Block 25) 256KB Code Flash block0 */

0x0117FFFF, /* (Block 26) 256KB Code Flash block0 */

0x011BFFFF, /* (Block 27) 256KB Code Flash block0 */

0x011FFFFF, /* (Block 28) 256KB Code Flash block0 */

0x0123FFFF, /* (Block 29) 256KB Code Flash block0 */

0x0127FFFF /* (Block 30) 256KB Code Flash block0 */

};

/* index of block which must not be accessed in demo*/

/* shall not access to BAF block and the blocks in the same partition with block storing code*/

#ifdef RAM_TARGET

const UINT32 SKIP_BLOCK_IDX[SKIP_IDX_NUM] = /* This has not been modified for the MPC5746C */

{

/* BLOCK IDX must be RWW Partition */

0xFF, /* No BAF block (Boot Assist Flash)*/

0x4,

0x5,

};

#endif

#ifdef FLASH_TARGET

const UINT32 SKIP_BLOCK_IDX[SKIP_IDX_NUM] =

{

/* SMALL BLOCKS */

0,

1,

2,

3,

4,

5,

6,

7,

8,

9,

10,

/* MID BLOCKS

11,

12,

13,

14,

15,

16,

17,

18, */

/* HIGH BLOCKS */

19,

20,

/* 256 KB BLOCKS */

21,

22,

23,

24,

25,

26,

27,

28,

29,

30

};

#endif

/* Initialize Memory region information */

void InitMemRegionInfo(PMEM_REGION_INFO pMemRegionInfo)

{

}

/************************************************************************

* (c) Copyright Freescale Semiconductor, 2012-2014 *

* All Rights Reserved *

*************************************************************************

*************************************************************************

* *

* Standard Software Driver for C55 *

* *

* FILE NAME : block_mpc57xx.h *

* DATE : 09.19.2014 *

* *

* AUTHOR : FPT Team *

* E-mail : r56611@freescale.com *

* *

************************************************************************/

/******************************* CHANGES ********************************

1.0.0 12.29.2011 FPT Team Initial Version for RTM version

***********************************************************************/

#ifndef __BLOCK_MPC57XX__

#define __BLOCK_MPC57XX__

#include "demo_common.h"

#include "C:/PRJ_MPC5746C/src/Flash_Driver/include/ssd_c55.h"

#include "c55flash_mpc57xx.h"

/* Lock State */

#define UNLOCK_LOW_BLOCKS 0x00000000

#define UNLOCK_MID_BLOCKS 0x00000000

#define UNLOCK_HIGH_BLOCKS 0x00000000

#ifdef RAM_TARGET

#define UNLOCK_FIRST256_BLOCKS 0x00000000

#endif

#ifdef FLASH_TARGET

#define UNLOCK_FIRST256_BLOCKS 0x000000FF

#endif

#define UNLOCK_SECOND256_BLOCKS 0x00000000

/* bit mask for block select for each address space */

/* need to un-select the blocks which are not accessed in demo*/

#define ALL_LOW_BLOCK_SEL (~UNLOCK_LOW_BLOCKS)

#define ALL_MID_BLOCK_SEL (~UNLOCK_MID_BLOCKS)

#define ALL_HIGH_BLOCK_SEL (~UNLOCK_HIGH_BLOCKS)

#define ALL_FIRST256_BLOCK_SEL (~UNLOCK_FIRST256_BLOCKS)

#define ALL_SECOND256_BLOCK_SEL (~UNLOCK_SECOND256_BLOCKS)

/* index of block that should not be accessed in demo code*/

#ifdef RAM_TARGET

#define SKIP_IDX_NUM 0x3 /* I don't know about this yet */

#endif

#ifdef FLASH_TARGET

#define SKIP_IDX_NUM 23

#endif

/* macros to simulate RWE and ERR */

#define EER_ADDR 0x00F94002 /* Must correspond to the RWE_MID_SEL BLOCK Below */

#define RWE_ADDR 0x00F94002 /* Must correspond to the RWE_MID_SEL BLOCK Below */

#define RWE_LOW_SEL 0x0

#define RWE_MID_SEL 0x1 /* 0x1, 0x2, 0x4, 0x8, 0x10, 0x20, 0x40, 0x80 */

#define RWE_HIGH_SEL 0x0

#define RWE_FIRST256_SEL 0x0

#define RWE_SECOND256_SEL 0x0

extern const UINT32 BLOCK_START_ADDRS[NUM_BLOCK_ALL];

extern const UINT32 BLOCK_END_ADDRS[NUM_BLOCK_ALL];

extern const UINT32 SKIP_BLOCK_IDX[SKIP_IDX_NUM];

extern void InitMemRegionInfo(PMEM_REGION_INFO pMemRegionInfo);

#endif /* End of (__BLOCK_MPC57XX__) */

/************************************************************************

* (c) Copyright Freescale Semiconductor, 2012-2014 *

* All Rights Reserved *

*************************************************************************

*************************************************************************

* *

* Standard Software Driver for C55 *

* *

* FILE NAME : c55flash_mpc5746m *

* DATE : 09.19.2014 *

* *

* AUTHOR : FPT Team *

* E-mail : r56611@freescale.com *

* *

************************************************************************/

/******************************* CHANGES ********************************

1.0.0 12.29.2011 FPT Team Initial Version for RTM version

***********************************************************************/

#ifndef _C55FLASH_MPC5777C_

#define _C55FLASH_MPC5777C_

/* Derivative defination */

#define MPC5746C

/************************************************************************

* hardware dependent configuration

************************************************************************/

#define C55_REG_BASE 0xFFFE0000 /* #define C55FMC (*(volatile struct C55FMC_tag *) 0xFFFE0000UL) */ /* C55 Flash Main Control */

#define MAIN_ARRAY_BASE 0x00404000 /* 3MB Flash Array plus 16 KB UTEST space. So Main Array starts after UTEST */

#define UTEST_ARRAY_BASE 0x00400000 /* 0x00400000 - 0x00403FFF*/

#define UTEST_ARRAY_SIZE 0x00004000 /* 0x00400000 - 0x00403FFF*/

#define C55_PROGRAMMABLE_SIZE 0x80 /* 128 Bytes */

/* block number for each address space */

#define NUM_LOW_BLOCK 11 /* Block Numbers 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10 */ /* Partition(s) 0 & 1 */

#define NUM_MID_BLOCK 8 /* Block Numbers 0, 1, 2, 3, 4, 5, 6, 7 */ /* Partition(s) 2 & 3 */

#define NUM_HIGH_BLOCK 2 /* Block Numbers 0 - 1 */ /* Partition(s) 4 & 5 */

#define NUM_256K_BLOCK_FIRST 10 /* Block Numbers 0 - 9 */ /* Partition(s) 6 & 7 */

#define NUM_256K_BLOCK_SECOND 0 /* Block Numbers ??? */ /* ??? */

#define NUM_BLOCK_ALL (NUM_LOW_BLOCK + NUM_MID_BLOCK + NUM_HIGH_BLOCK + NUM_256K_BLOCK_FIRST + NUM_256K_BLOCK_SECOND)

#define SWT_REG 0xFC050000UL /* 0xFFF34000UL */ /* Software Watchdog Timer #define SWT_0 (*(volatile struct SWT_tag *) 0xFC050000UL) */

#define SWT_REG_A 0xFC054000UL /* 0xFFF38000UL */ /* Software Watchdog Timer #define SWT_1 (*(volatile struct SWT_tag *) 0xFC054000UL) */

#define SWT_CR_OFFSET 0x00000000UL /* 0 SWT Control Register (SWT_CR) 32 R/W See section 50.4.1/2165 */

#define SWT_SR_OFFSET 0x00000010UL /* 10 SWT Service Register (SWT_SR) 32 W 0000_0000h 50.4.5/2170 */

/* Macro data cache avaiable in the main core */

//#define DCACHE_AVAILABLE 1

#define FLASH_TARGET 1

/* Flash controller definition */

#define FLASH_FMC 0xFC030000 /* #define PFLASH (*(volatile struct PFLASH_tag *) 0xFC030000UL) */

/* Offsets of Platform Flash Configuration Register 1, 2, 3 */

#define FLASH_PFCR1 0 /* Offset address of PFLASH_PFCR1 */ /* 0 Platform Flash Configuration Register 1 (PFLASH_PFCR1) 32 R/W 0000_0601h 71.5.1/3007 */

#define FLASH_PFCR2 4 /* Offset address of PFLASH_PFCR2 */ /* 4 Platform Flash Configuration Register 2 (PFLASH_PFCR2) 32 R/W 0000_0001h 71.5.2/3010 */

#define FLASH_PFCR3 8 /* Offset address of PFLASH_PFCR3 */ /* 8 Platform Flash Configuration Register 3 (PFLASH_PFCR3) 32 R/W 0000_0000h 71.5.3/3013 */

#define FLASH_FMC_BFEN 0x00000001 /* Enable PBFEN bit */ /* PFLASH Line Read Buffers Enable */

#endif /* End of (_C55FLASH_MPC5777C_) */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found part of the answer here Tips to run EEE Driver with freeRTOS in MPC5746C

The problem is that there is no support for the S32 compiler, so I had to disable DCACHE.

Is there a way to enable DCACHE for the S32 environment?

#if DCACHE_AVAILABLE

#include "C:/PRJ_MPC5746C/src/Flash_Driver/include/ssd_types.h"

#ifdef __ghs__

#include <ppc_ghs.h>

#define E200CORE_SYNC() __MSYNC() /* Memory synchronize */

#define E200CORE_ISYNC() __ISYNC() /* Instruction synchronize */

#define E200CORE_SPR_GET(lhs, reg) {lhs = __MFSPR(reg);} /* read from special register*/

#define E200CORE_SPR_SET(reg, val) __MTSPR(reg, val) /* write to special register*/

#elif (defined __CWCC__)

#define E200CORE_SYNC() asm(" msync") /* Memory synchronize */

#define E200CORE_ISYNC() asm ("isync") /* Instruction synchronize */

#define E200CORE_SPR_GET(lhs, reg) {register _t; asm{ mfspr _t, reg } lhs = _t; } /* read from special register*/

#define E200CORE_SPR_SET(reg, val) {register _t = val; asm{ mtspr reg, _t } } /* write to special register*/

#elif (defined __DCC__)

#include <diab/asm.h>

#define E200CORE_SYNC() __msync() /* Memory synchronize */

#define E200CORE_ISYNC() __isync() /* Instruction synchronize */

#define E200CORE_SPR_GET(lhs, reg) {lhs = __mfspr(reg);} /* read from special register*/

#define E200CORE_SPR_SET(reg, val) __mtspr(reg, val) /* write to special register*/

#else

#error "This compiler is not supported"

#endif